# MIXED SIGNAL FAULT SIMULATOR: COMPARISONS OF HARDWARE AND SIMULATION RESULTS

By

Aaron E. Case

A thesis submitted to the faculty of The University of North Carolina at Charlotte. in partial fulfillment of the requirements for the degree of Masters of Science in the Department of Electrical and Computer Engineering

Charlotte

2002

| Approved by:       |  |

|--------------------|--|

| Dr. Thomas Weldon  |  |

| Dr. Charles Stroud |  |

| Dr. David Binkley  |  |

©2002 Aaron Earnest Case ALL RIGHTS RESERVED

#### **ABSTRACT**

AARON EARNEST CASE. Mixed Signal Fault Simulator: Comparisons of Hardware and Simulation Results. (under the direction of DR. THOMAS PAUL WELDON)

This thesis describes a mixed signal fault simulator and compares simulated results to theoretical and hardware experimental results. The fault simulator takes a SPICE net list file as input and produces, as output, the circuit's behavior under certain fault conditions in order to establish the fault coverage of combinations of test waveforms and output metrics. The present form of the fault simulator includes catastrophic faults, typically open or short circuits. To demonstrate the efficacy of the fault simulator, simulated results were compared against hardware experimental results to verify the accuracy of the simulator for the specific case of a BiQuad filter. In this thesis, the focus is on the development of the analog portion of the mixed signal fault simulator, since the treatment of the digital portions of the circuit is well known and well defined.

#### **ACKNOWLEDGEMENTS**

I would first and foremost like to thank Dr. Thomas P. Weldon for affording me the opportunity to work under his direction on the DARPA neo-CAD project as well as all direction and tutelage involved therein. I would also like to thank Dr. Thomas P. Weldon for all the challenging and rewarding course work over the past few years. I would like to thank Dr. Stroud for material support. I would like to thank Dr. Makki for encouraging and convincing me to enter the graduate program at UNC Charlotte. I would like to thank my fellow research assistants Clark Hopper, Steve Tucker, Jason Morton, Ana Maria, Deepa Patel, Ramsey Hourani, and Konrad Miehle for their respective contributions and assistance. Supported by Defense Advanced Research Program Administration (DARPA) and managed by the Sensors Directorate of the Air Force Research Laboratory, USAF, Wright-Patterson AFB, OH 45433-6543.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                      | ix   |

|----------------------------------------------------------------------|------|

| LIST OF TABLES                                                       | xii  |

| LIST OF ABREVIATIONS                                                 | xiii |

| CHAPTER 1: INTRODUCTION                                              |      |

| 1.1 Current State of the Art                                         | 3    |

| 1.2 Overview of Current Challenges and Solutions to Fault Simulation | 6    |

| 1.3 Statement of Problem                                             | 8    |

| CHAPTER 2: FAULT SIMULATION FUNCTIONAL OVERVIEW                      |      |

| 2.1 BIST Framework                                                   | 9    |

| 2.2 Fault Simulator Functional Flow                                  | 10   |

| 2.3 Fault Simulation Architecture                                    | 15   |

| 2.3.1 SPICE Input                                                    | 15   |

| 2.3.2 Parser                                                         | 17   |

| 2.3.2.1 Component Statistics                                         | 17   |

| 2.3.3 Test Pattern Generation                                        | 20   |

| 2.3.4 Fault File Generation                                          | 20   |

| 2.3.5 SPICE Engine                                                   | 21   |

| 2.3.6 ORA                                                            | 22   |

| 2.3.7 Statistical Analysis                                           | 22   |

| 2.4 Class Objects                                                    | 22   |

| 2.4.1 Class Resistor                                                 | 23   |

| 2.4.2 Class Inductor.                                                | 23   |

| 2.4.3 Class Capacitor          | 23 |

|--------------------------------|----|

| 2.4.4 Class Ora                | 23 |

| 2.4.5 Class Gsrc               | 23 |

| 2.4.6 Class Vsrc.              | 24 |

| 2.4.7 Class Circuit            | 24 |

| 2.4.8 Class DotEnds            | 24 |

| 2.4.9 Class Other              | 24 |

| 2.4.10 Class Xsubckt           | 25 |

| 2.4.11 Class CircuitStats      | 25 |

| 2.4.12 Class DotSubckt         | 25 |

| 2.4.13 Class Isrc              | 25 |

| 2.4.14 Class Comment           | 25 |

| 2.4.15 Class Esrc.             | 26 |

| 2.4.16 Class Statistics        | 26 |

| 2.4.17 Class Component         | 26 |

| 2.4.18 Class Mos               | 26 |

| 2.4.19 Class Faultlist         | 27 |

| 2.4.20 Class Tpg               | 27 |

| 2.4.21 Class Data              | 27 |

| 2.5.1 Computational Complexity | 27 |

| 2.5.2 Computational Time       | 27 |

| 2.5.3 Parallel Processing.     | 28 |

| 2.6 Faultsim                   | 29 |

# CHAPTER 3: VERIFICATION WITH HARDWARE

| 3.1 Biquadratic Filter Circuit                  | 31         |

|-------------------------------------------------|------------|

| 3.2 Modeling the Biquad Efficiently             | 33         |

| 3.3 Theoretical Results (Hand Calculations)     | 36         |

| 3.3.1 Calculation for Specific Fault Conditions | 37         |

| 3.3.1.1 S <sub>out</sub> Floating Point         | 40         |

| 3.3.1.2 S <sub>del</sub> Floating Point         | 11         |

| 3.3.1.3 S <sub>mag</sub> Floating Point         | 41         |

| 3.3.1.4 Summary of Floating Point Calculations  | 43         |

| 3.3.2 Digital ORA Metrics                       | 44         |

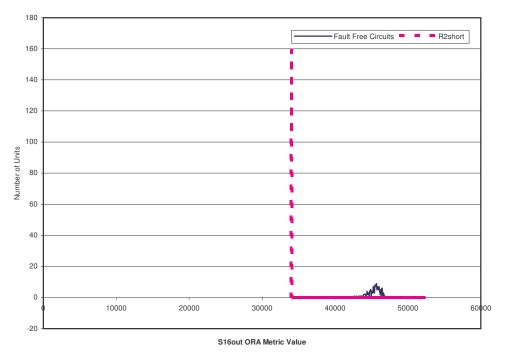

| 3.3.2.1 S <sub>16out</sub> Digital Value        | 44         |

| 3.3.2.2 S <sub>16del</sub> Digital Value        | 45         |

| 3.3.2.3 S <sub>16mag</sub> Digital Values       | 46         |

| 3.3.2.4 Summary of Digital Calculations4        | 16         |

| 3.4 Simulation Data for Biquad Filter Circuit   | <b>ļ</b> 7 |

| 3.4.1 Analog Results for Fault Simulator        | 18         |

| 3.4.2 Digital Results for Fault Simulator5      | 53         |

| 3.5 Comparison with Experimental Hardware       | 58         |

| 3.6 Good Circuit Result Confirmation6           | 60         |

| 3.7 Conclusion6                                 | 52         |

| CHAPTER 4: POTENTIAL FUTURE DIRECTIONS          |            |

| 4.1 Speeding up Fault Simulation64              | 4          |

| 4.2 Fault Coverage67                            | 7          |

|                                                 |            |

| 4.3 Receiver Operating Characteristics                                                                                                           | 70  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4 Bhattacharyya Distance and Fast TPG Pattern Searching                                                                                        | 73  |

| REFERENCES                                                                                                                                       | 77  |

| APPENDIX A: Class Libraries and their Functions                                                                                                  | 80  |

| APPENDIX B: List of TPG Waveforms                                                                                                                | 82  |

| APPENDIX C: OpAmp1 Spice Net List                                                                                                                | 84  |

| APPENDIX D: BiQuad Net List                                                                                                                      | 85  |

| APPENDIX E: Faultsim and Class Library Manual                                                                                                    | 86  |

| APPENDIX F: Histograms for Each Fault vs. Fault-Free for S <sub>16out</sub> and S <sub>16mag</sub> Metrics for Each Fault with 19.5 kHz Count-up | 5   |

| Waveform                                                                                                                                         | 135 |

#### LIST OF FIGURES

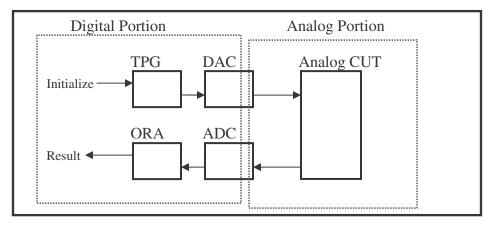

- FIGURE 2.1 Built in self test (BIST) framework.

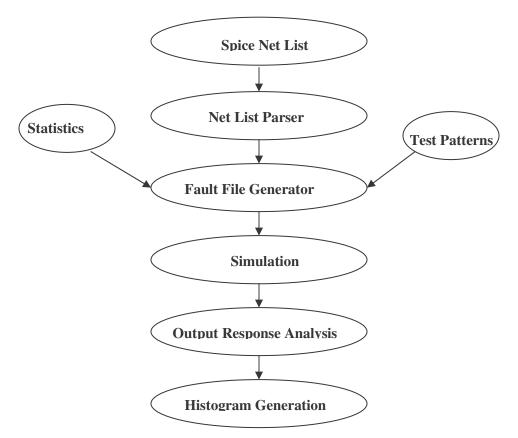

- FIGURE 2.2 Fault simulator functional flow diagram.

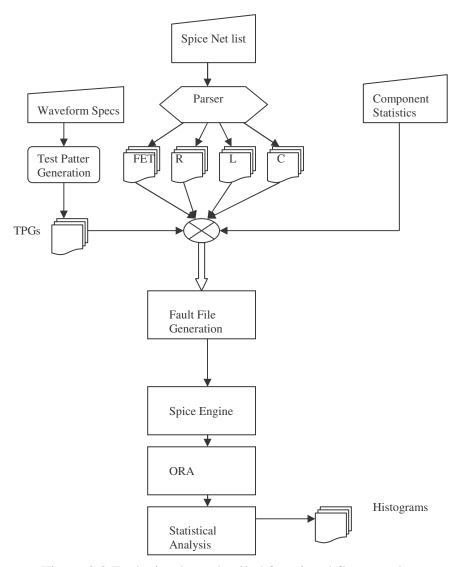

- FIGURE 2.3 Fault simulator detailed functional flow graph.

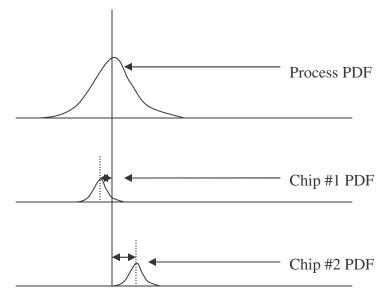

- FIGURE 2.4 Statistical models showing process pdf (probability density function) in upper trace and two lower traces illustrating single chip pdf's for two different chips. Lower two traces indicate component variations within a single chip or integrated circuit.

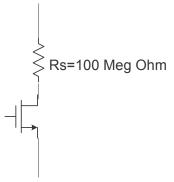

- FIGURE 2.5 Stuck-off fault for transistor illustrating 100 M  $\Omega$  series resistor used to implement fault.

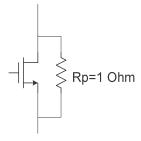

- FIGURE 2.6 Stuck-on fault for transistor illustrating 1 ohm parallel source drain resistor used to implement fault.

- FIGURE 2.7 Faultsim help screen showing description of command-line parameters and example command-line.

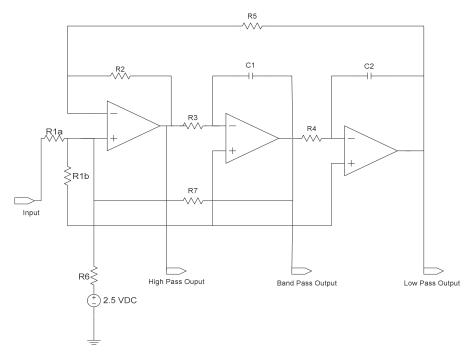

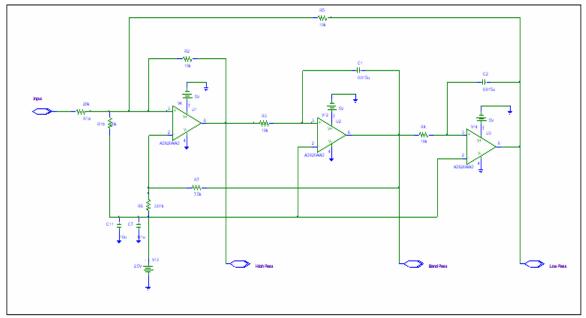

- FIGURE 3.1 BiQuad filter circuit used for benchmarking fault simulator against hardware.

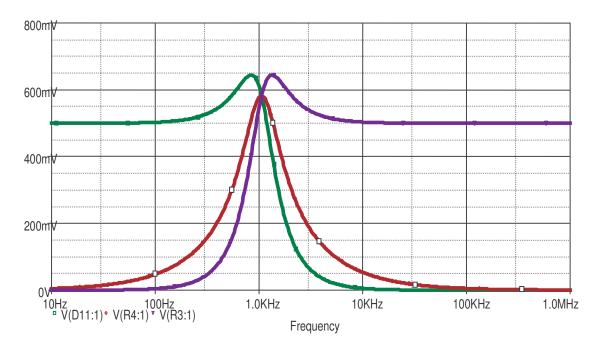

- FIGURE 3.2 Frequency response of BiQuad filter shown in Fig. 3.1 with 1 kHz cutoff frequency for high pass low pass and band pass.

- FIGURE 3.3 BiQuad hardware implementation using AD820 amplifier.

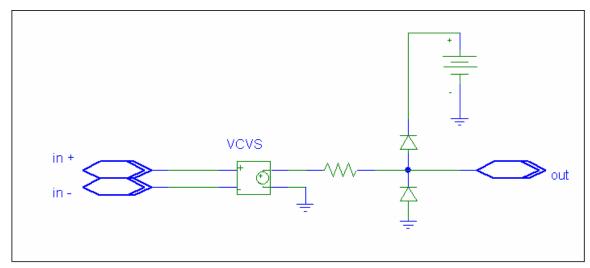

- FIGURE 3.4 Emulation of AD820A amplifier used in BiQuad circuit design ideal voltage controlled voltage source, two diodes and output impedance resistor.

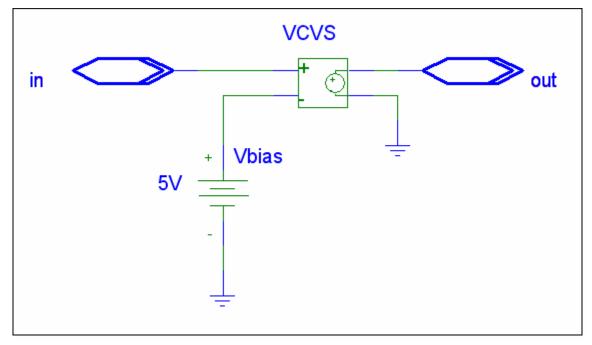

- FIGURE 3.5 Inverting amplifier for input of BiQuad circuit used to translate 0 to 5 volt input to 5 to 0 volt output. Gain of VCVS is -1.

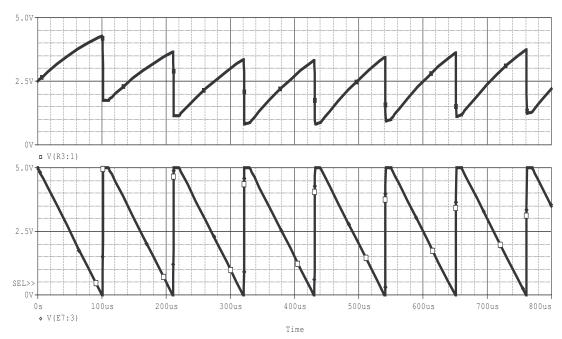

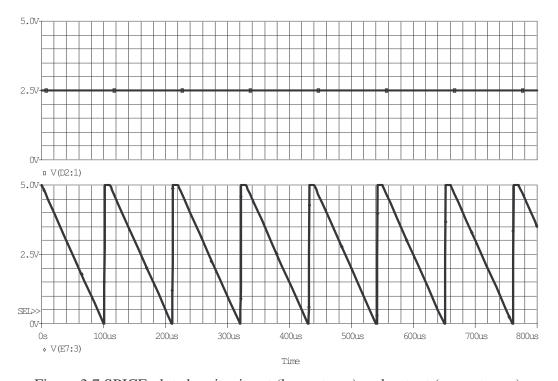

- FIGURE 3.6 SPICE simulation of circuit of BiQuad showing input (lower trace) and output (upper trace). Transient output response due to initial conditions is visible in the output plot.

- FIGURE 3.7 SPICE plot showing input (lower trace) and output (upper trace) of faulty BiQuad circuit with 2.5-V DC output condition.

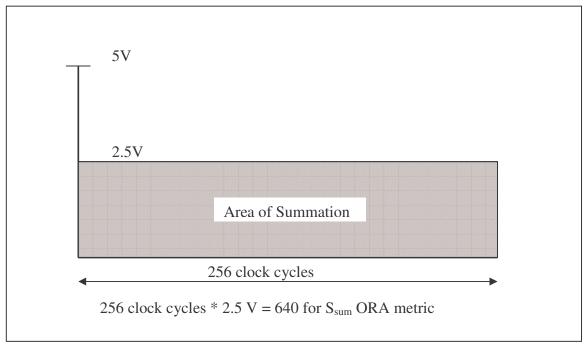

- FIGURE 3.8 Illustration showing area corresponding to the fault for 2.5-V output condition of Fig. 3.7 over 256 clock cycles for computing S<sub>out</sub> metric. The area is 2.5x256=640.

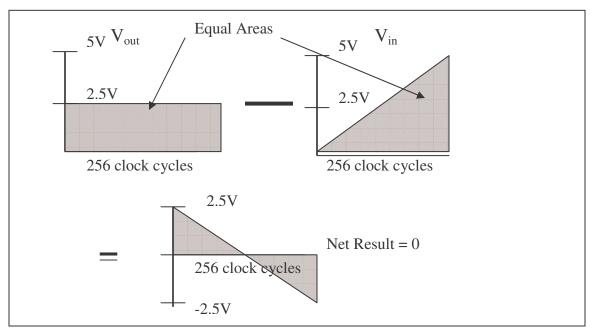

- FIGURE 3.9 Illustration showing area corresponding to the fault for 2.5-V output condition over 256 clock cycles for computing  $S_{del}$  metric. The top left plot is the input waveform, the top right plot is the output waveform, and the bottom waveform is the resultant subtraction of the two upper plots. The lower plot with equal areas above and below the time axis have a net result of zero.

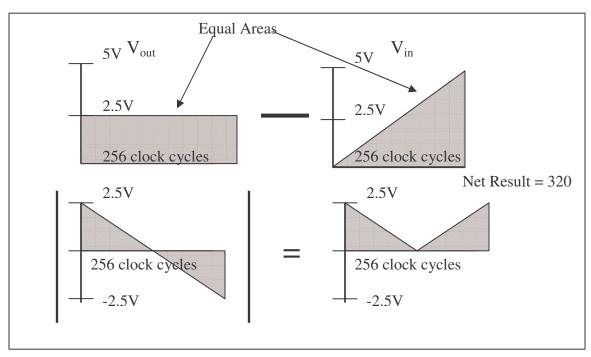

- FIGURE 3.10 Illustration showing area summed for 2.5-V output condition over 256 clock cycles for  $S_{mag}$  metric. Top left is input waveform, top right is output waveform, bottom left is result of subtraction of output from input, and bottom right is magnitude of bottom left.

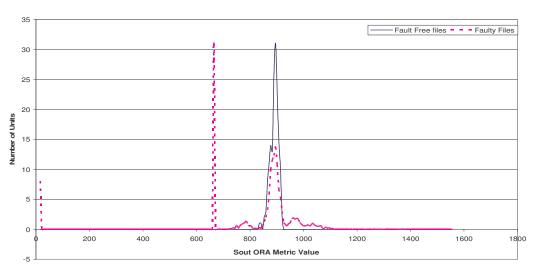

- FIGURE 3.11 Fault simulator results for analog  $S_{out}$  ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which is the histogram for fault-free circuits.

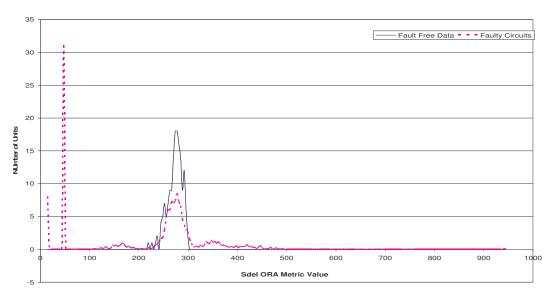

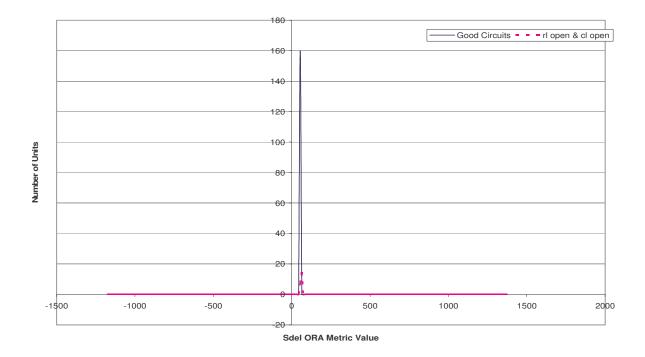

- FIGURE 3.12 Fault simulator results for analog  $S_{del}$  ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which, is the histogram for fault-free circuits.

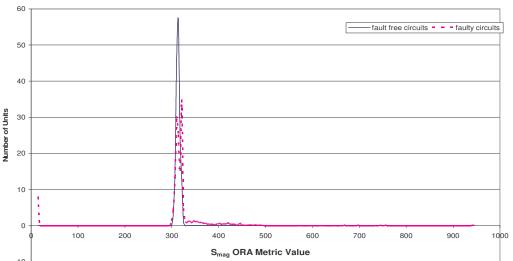

- FIGURE 3.13 Fault simulator results for Analog  $S_{mag}$  ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which is the histogram for fault-free circuits.

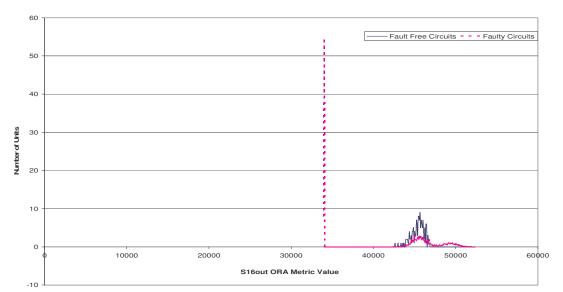

- FIGURE 3.14 Fault simulator results for analog  $S_{16out}$  ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which is the histogram for fault-free circuits.

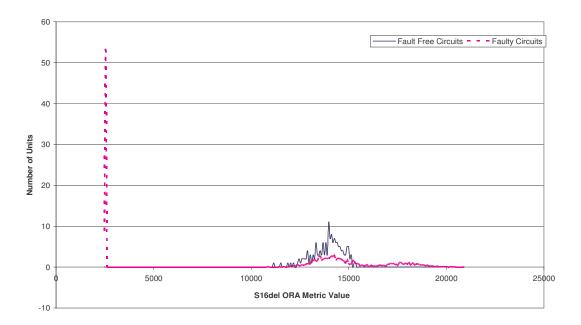

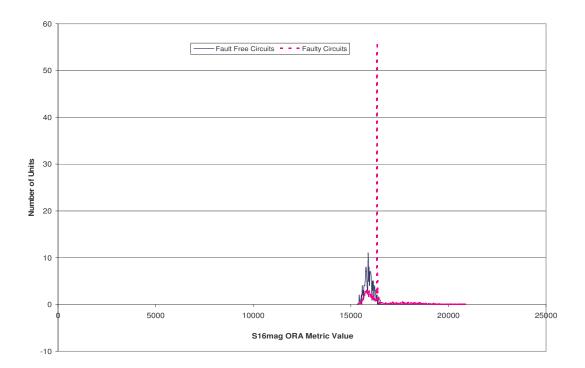

- FIGURE 3.15 Fault simulator results for analog S<sub>16del</sub> ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which is the histogram for fault-free circuits.

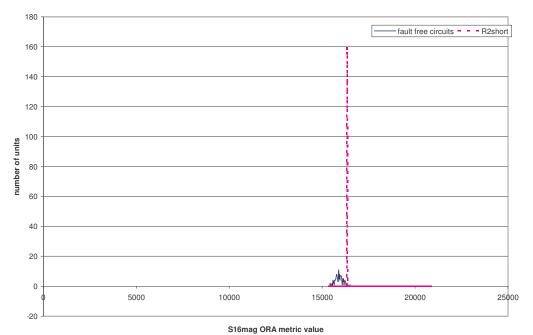

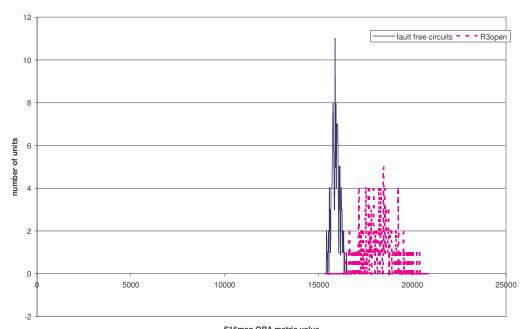

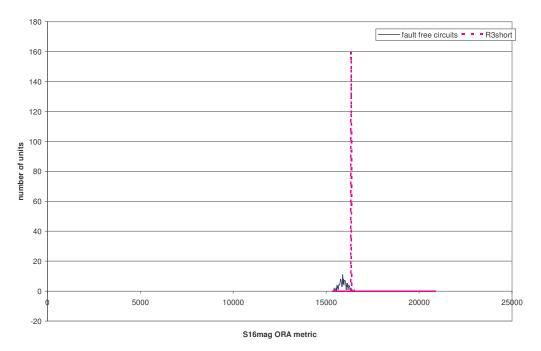

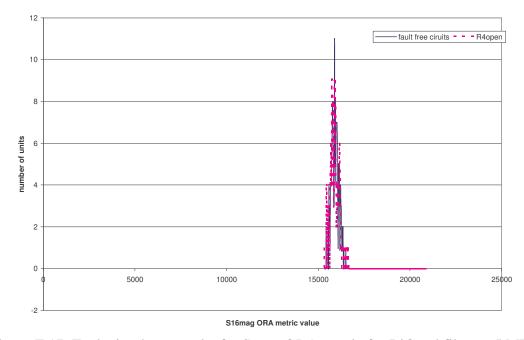

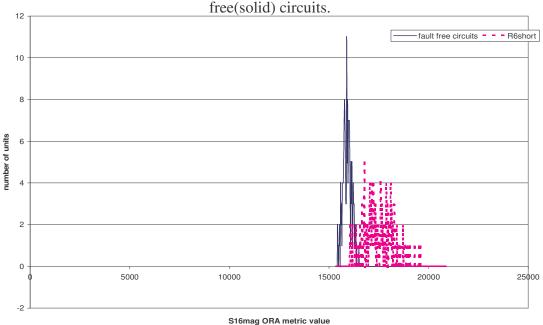

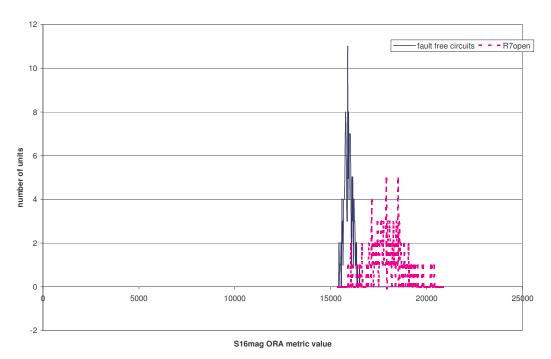

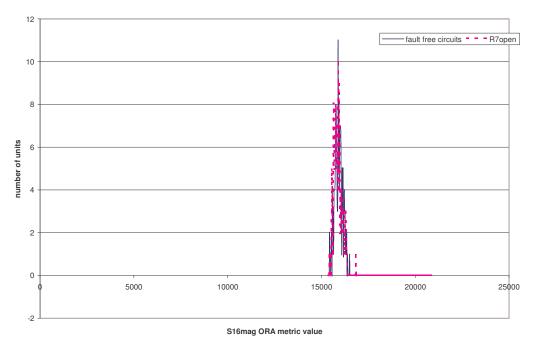

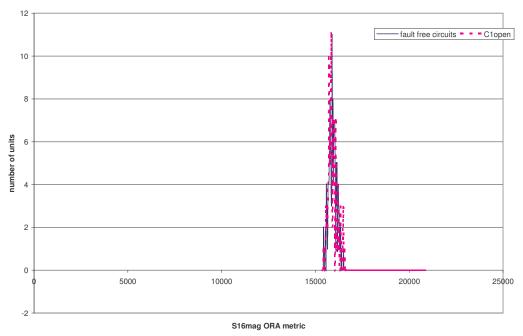

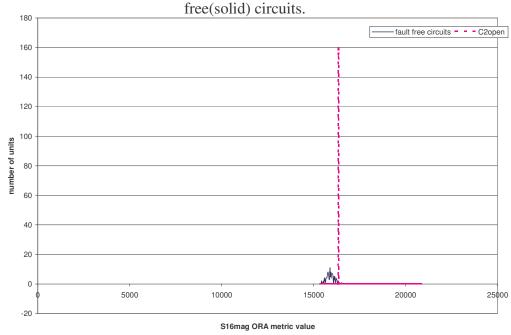

- FIGURE 3.16 Fault simulator results for analog S<sub>16mag</sub> ORA metric for BiQuad filter at 5 MHz clock frequency (19.5 kHz effective frequency), Cup waveform, 5 V amplitude, 2.5 V offset, and 0-5V output range. The dotted histogram is a composite of all faults rescaled and normalized relative to the soled histogram which is the histogram for fault-free circuits.

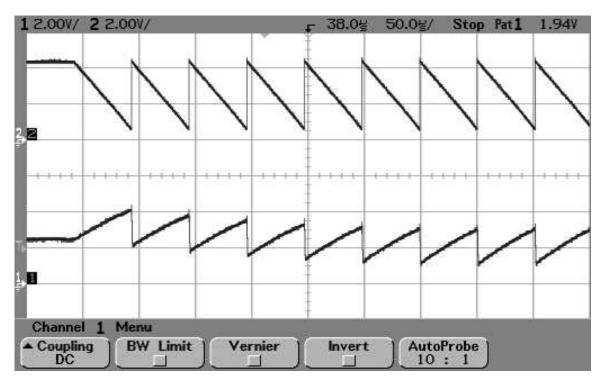

- FIGURE 3.17 Oscilloscope plot showing presence of transient effect on 5MHz Cup waveform with 5Vpp input on BiQuad filter (compare to SPICE plot Fig. 3.6). Upper trace is 0 to 5 V Cup input TPG waveform (after inverting amp of Fig. 3.5), showing transient behavior within first 4 or 5 cycles of saw-tooth waveform.

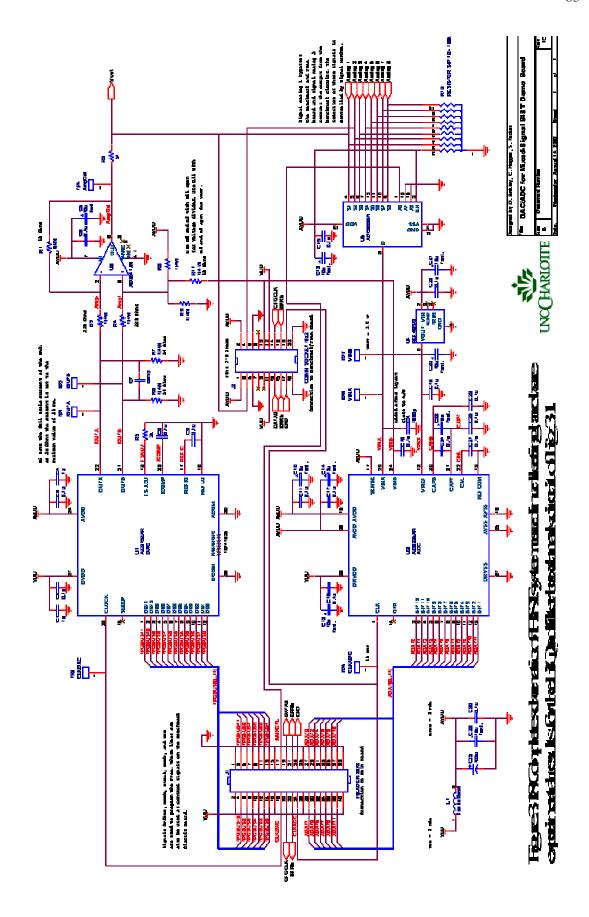

- FIGURE 3.18 Complete schematic of BIST system used in collecting hardware experimental results for the BiQuad filter benchmark circuit of Fig. 3.1.

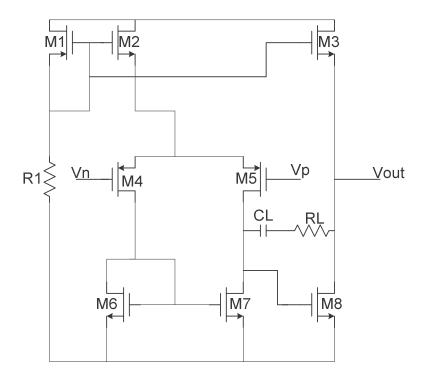

- FIGURE 4.1 Operational amplifier circuit (OpAmp1).

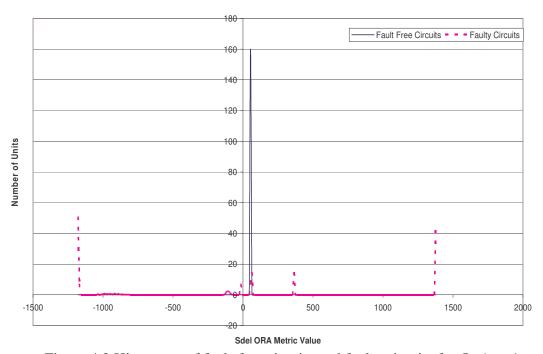

- FIGURE 4.2 Histogram of fault-free circuits and faulty circuits for OpAmp1 with 200 mV Cup waveform at 10 kHz clock frequency.

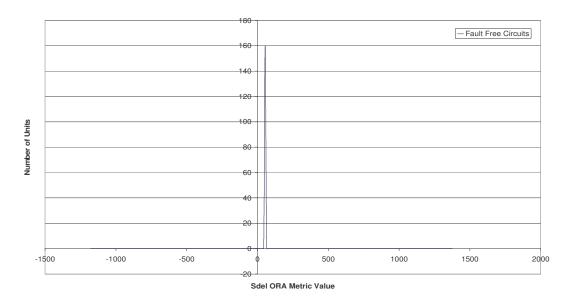

- FIGURE 4.3 Histogram of fault-free circuits for OpAmp1 with 200 mV Cup waveform at 10 kHz clock frequency.

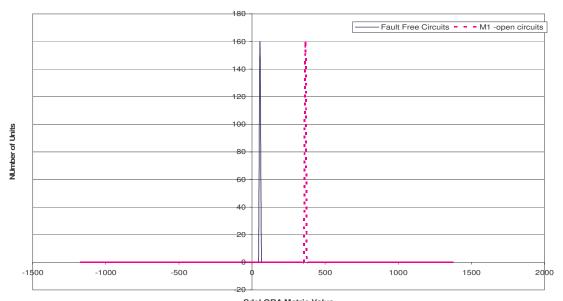

- FIGURE 4.4 Histogram of fault-free circuits and circuits with M1 open for OpAmp1 with 200 mV Cup waveform at 10 kHz clock frequency.

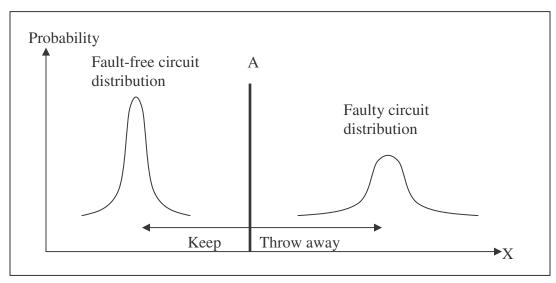

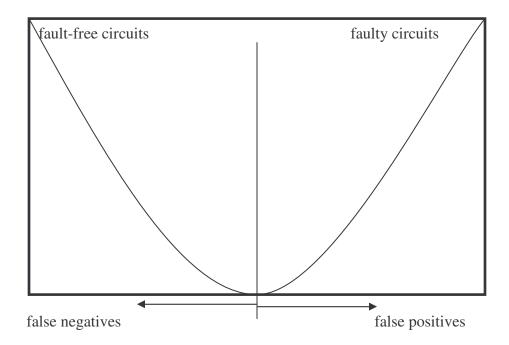

- FIGURE 4.5 Histogram illustrating false positives and false negatives.

- FIGURE 4.6 Receiver operating curve.

# LIST OF TABLES

| TABLE 2.1  | Floating point ORA metrics                                                                                                                                                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE 2.2  | Digital ORA metrics                                                                                                                                                                                |

| TABLE 2.3  | Process statistics                                                                                                                                                                                 |

| TABLE 3.1  | Fault List for BiQuad filter circuit simulation                                                                                                                                                    |

| TABLE 3.2  | List of Specific Components and Faults for ORA Confirmation were $V_{\text{out}}$ is a constant 2.5 VDC                                                                                            |

| TABLE 3.3  | The theoretical floating point values for ORA metrics $S_{out}$ , $S_{del}$ , and $S_{mag}$ for the fault in Table 3.2 with 2.5-VDC output with saw-tooth input over one cycle                     |

| TABLE 3.4  | The theoretical digital values for ORA metrics $S_{16\text{out}}$ , $S_{16\text{del}}$ , and $S_{16\text{mag}}$ for the fault in Table 3.2 with 2.5-VDC output with saw-tooth input over one cycle |

| TABLE 3.5  | Faults with only slight effect on the output of BiQuad filter for count-up waveform at 19.5 kHz                                                                                                    |

| TABLE 3.6  | $S_{\text{out}}$ comparison of analog theoretical values against fault simulator results                                                                                                           |

| TABLE 3.7  | $S_{\text{del}}$ analog theoretical values against fault simulator results                                                                                                                         |

| TABLE 3.8  | $S_{\text{mag}}$ analog theoretical values against fault simulator results                                                                                                                         |

| TABLE 3.9  | $S_{16out}$ digital theoretical values against fault simulator results.                                                                                                                            |

| TABLE 3.10 | $S_{16del}$ digital theoretical values against fault simulator results                                                                                                                             |

| TABLE 3.11 | $S_{16\text{mag}}$ digital theoretical values against fault simulator results                                                                                                                      |

| TABLE 3.12 | Comparison of experimental hardware and simulations for $S_{16out}$ ORA metric showing difference between means and percent difference                                                             |

| TABLE 3.13 | Comparison of experimental hardware and simulations for $S_{16 mag}$ ORA metric showing difference between means and percent difference                                                            |

# LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit

BIST Built in Self Test

BJT Bipolar Junction Transistor

CAD Computer Aided Design

CUT Circuit Under Test

DFT Design for Test

DUT Device Under Test

FET Field Effect Transistor

FPGA Field Programmable Gate Arrays

HBIST Hybrid Built in Self Test

IC Integrated Circuit

MOS Metal Oxide Semiconductor

ORA Output Response Analysis

ROC Receiver Operating Characteristics

VCVS Voltage Controlled Voltage Source

VLSI Very Large Scale Integrated

SFA Statistical Fault Analyzer

SPICE Simulation Program with Integrated Circuit Emphasis

SoC System on a Chip

TPG Test Pattern Generator

pdf Probability Density Function

#### CHAPTER 1: INTRODUCTION

This thesis presents a mixed signal fault simulator for built-in self-test (BIST) and gives experimental hardware and simulation results that verify the performance of the simulator. The focus of this effort is on the analog portion of the mixed signal fault simulator since the methodology for digital portions of a mixed signal system are well known. The thesis begins with an introduction of the relevance of fault simulation and how it fits into the overall product cycle. Next, the architecture and methods used to develop the fault simulator are discussed. Then, simulator results are compared with hardware results to validate the fault simulator models and techniques. Finally, directions for future work are offered. In the following, the background of the fault simulator is given. Details on the simulator and experimental results are given in subsequent chapters.

To place the need for a fault simulator in a larger context, consider a typical manufacturing process that has at some point a verification stage, whereby it is determined that a product meets specifications. This stage of production should seek to pass products that are good and eliminate the products that are bad, and only the products that are bad. In the process of product verification there are inevitably four categories of products found [21]. In the first category, bad units that are found to be good in production are known as false positives. This category can be costly to a firm through replacement costs, loss of reputation, and ensuing loss of market share. The false-

positive portion would ideally be zero for any enterprise as it is a liability in the mart of competitive commerce. In the second category, units that are found to be bad, and are bad, are minimally damaging to an enterprise in the sense that there is a loss of materials. In the third category, good units that are found to be bad in production are known as false negatives [21]. False negatives do not greatly damage a firm's reputation, but cause loss of resources and time. In the final category, good units that are found to be good in production are the yield of an enterprise. So, it can be seen that any product verification process should limit any erroneous prognosis as well as bad products. In this manufacturing context, the fault simulator is a tool for designing built in self test (BIST) to minimize losses due to false positives and false negatives.

In addition, the complexity of mixed signal and analog integrated circuits lead to complicated verification requirements [18]. In particular, it is difficult to predict how analog portions of a mixed signal system will behave under variable circumstances such as component variations, faults, and different test metrics. Such predictions of system behavior, either for use with external testing equipment or for use with built-in self-test architectures, can be generated by a fault simulator early in the design and test cycle. Through such fault simulation, fault coverage can be determined for a set of test patterns and output metrics to ensure that a circuit is free of manufacturing defects.

In the following, we first review the current state of the art. Then we give an overview of current challenges in fault simulation. Finally, the problem addressed in this thesis is stated.

#### 1.1 Current State of the Art

In digital portions of a mixed signal circuit, fault modeling is well established. Digital fault modeling can be classified into two categories, gate level fault modeling and transistor level fault modeling [21, 8, 2]. In digital circuits there are two types of faults, stuck-at-one(sa1) and stuck-at-zero(sa0)[2]. Both levels of digital fault modeling utilize these types of faults. In gate level fault modeling, the stuck at faults are exercised at the gate inputs and outputs. In transistor level fault modeling required for CMOS technology, stuck at faults are modeled at the transistor level rather than just the gate level, giving a more complex yet comprehensive picture of fault conditions.

There has been much done in the area of digital fault simulation and modeling, but much less work in the realm of analog fault simulation [8]. The lack of a mature analog fault simulator can be partly attributed to the lack of mature fault models for analog circuits [7]. Furthermore, modeling and isolating faults in analog circuits is one if the most difficult tasks in diagnostic engineering [8].

The work on analog fault models can be classified into two categories, catastrophic faults and parametric faults [26]. Catastrophic faults, also referred to as hard faults, are the analog equivalents of stuck at faults in the digital domain. Analog hard faults occur when the terminal nodes of the component are stuck short or stuck open.

Parametric faults are defined as any variation of the component values outside the acceptable performance range or tolerance limits [27].

The current models used for catastrophic faults of analog circuits include the use of high and low resistances to model shorts and opens at the component terminals as later shown in Figs. 2.5 and 2.6[27, 28]. The resistive and capacitive components have a 1  $\Omega$

resistance in parallel ( $R_p = 1 \Omega$ ) for shorts and a 100 M $\Omega$  resistance in series ( $R_s = 100 M\Omega$ ) for opens. Similarly, the MOSFET is faulted in much the same manner across the source and drain only. In contrast, the BJT has a stuck-open and stuck-short fault between each of its three terminals, collector, emitter, and base [27].

Many different methods have been proposed for analog fault simulation. One notable method uses DC transfer function testing to test and isolate faults [10]. While DC testing is promising in cost and compact in layout size, the method has lower fault coverage at the macro level and is not viable at the transistor level [10]. DC testing does provide for simpler fault modeling but, does not give adequate parametric fault coverage for many types of analog circuits [10].

A second method, behavioral fault simulation works well for simplifying and expediting analog fault simulation [4]. In behavioral fault modeling methods, the basic algorithm is the same as that for event-driven logic simulation, except that the fault simulation algorithm propagates fault lists along with logic values through gate level hardware descriptions [4]. Behavioral modeling is generally accepted as being faster but less accurate than other methods and does not lend itself well to analog fault modeling without acceptable levels of complication. However, behavioral modeling only works at the gate level and therefore will not lend itself to analog micro-modeling [4].

A third method, functional fault models also work well at simplifying digital fault modeling but are often too complex and don't offer high fault coverage at the transistor level for analog faults [8]. Functional fault models work on blocks of analog circuits and can therefore only diagnose a faulty block of components not individual component

failures. Furthermore, functional fault models only offer a limited number of output conditions for each fault given a predefined test vector.

Another analog fault modeling technique is the test-oscillation methodology. The oscillation methodology treats every analog sub-circuit as an oscillator for verification [9]. The technique tests the frequency response of the fundamental analog blocks against known frequencies for fault-free case to detect faults [9]. While the method is promising with respect to cost and area overhead, in most cases, the method is not generally applicable to all types of circuits without considerable modifications [9, 2, 5].

For any methodology, fault simulation is used to identify the best set of test vectors and output metric to be capable of finding of identifying the maximum number of faults in a circuit. Fault simulation allows investigation of the efficacy of different test vectors and output metrics. By using the fault simulator, the best test vector and output metrics can be identified for a particular system.

Although not recommended, fault simulation could be bypassed in the design of a system. In this case, the verification stages of chip manufacturing consist of blindly applying a signal and measuring a "good output" for a fault-free unit. Without fault simulation data, selecting test vectors for any testing architecture would be not be possible due to a lack of prior knowledge of circuit behavior under faulty conditions. The fault simulator on the other hand allows investigation of input/output behavior of any possible fault conditions for a variety of test vectors and output metrics.

At present, the state of the art for analog and mixed signal fault modeling has yet to witness the same success as digital fault modeling and test pattern generation [8]. The more primitive state of analog and mixed signal fault simulations and techniques can be

attributed to the complexity of fault modeling in an analog circuit versus digital circuits. Research in IC testing has produced various methods and products to approach the problem of analog fault modeling in mixed signal circuits but has yet to arrive at any widely accepted standard or method. The aforementioned technologies offer potential for analog fault modeling to close the gap on much more advanced digital fault modeling [2]. Thus, this thesis focuses on initial steps toward mixed-signal fault simulation.

Analog fault simulation and fault modeling present different, and more complex, challenges than digital fault modeling, due to the nature of analog circuits [26, 27]. The performance of analog portions of a mixed signal circuit are subject to parametric variations, in addition to catastrophic faults such as an open or a short. Any simulation or testing procedure for an analog circuit must include parametric variation of components, as well as catastrophic faults, in verification and test vector generation. Therefore, analog portions of a mixed signal IC present much more complex problems in testing and simulation, and thus are more costly in verification. In the next section, we give further overview of issues in fault simulation.

# 1.2 Overview of Current Challenges and Solutions to Fault Simulation

Although there has been much work in the area of digital fault simulation and fault modeling, analog fault simulation lags far behind that of digital fault simulation due to the complexity of analog fault simulation and analog IC verification [8]. Analog and mixed signal IC's require more time and money investment in fault modeling and simulation to achieve the same level of fault coverage as their digital counterparts [8]. The nature of an analog circuit makes testing, and testing decisions, considerably more complex. With a digital circuit, a test vector will indicate that a certain gate or transistor

is stuck at 0 or 1, but an analog test vector needs to indicate if a analog circuit is within a predetermined error bound [16]. Thus, one complicating problem in analog testing is where to draw the line, or threshold, for fault-free or faulty analog circuits as well as how to quantify the yield of fault-free circuits. In this, fault coverage can be defined as the number of detected faults divided by the total number of possible faults (i.e., in a fault list) [2].

An analog or mixed signal fault simulation can consider normal parametric variations in conjunction with catastrophic faults in fault simulation. To accurately estimate the probability distribution of how a fault-free circuit behaves, a large number of samples taken from parametrically randomized circuits is required. The range of values for any given output metric that are obtained for the randomized good circuit will indicate natural variations due to the fabrication and manufacturing process of the system. This parametric randomization also must be done for each injected fault to determine accurately the probability distribution of output metric values for each fault. The foregoing randomization for fault-free and faulty circuits, combined with need to evaluate the circuit with a multitude of waveforms, lead to very large simulation times even for the simplest of circuits. Simulation times on the order of weeks can be encountered with as few as 15 components, 30 faults, 200 randomizations, and 30 waveforms. In this example, there are  $(30+1)\times 200\times 30=186,000$  combinations. Therefore, an important issue in fault simulation considered by this thesis is reducing simulation times and developing techniques to accelerate computation, and these issues are partly addressed in the future work section.

#### 1.3 Statement of Problem

This thesis describes the design and testing of the analog portion of a mixed signal fault simulator. The simulator takes as input a SPICE file of a circuit under test (CUT) and produces, as output, statistical information on the behavior of the circuit under all fault conditions with a variety of candidate test pattern waveforms and output metrics. The raw output metric data of the simulator is post-processed into histograms that provide statistical fingerprints of a variety of output metrics for each potential catastrophic fault in the circuit. The output data and histograms can then be used to identify the best input stimuli, or test pattern waveforms, and the best output metrics for testing a hardware version of the circuit.

The present fault simulator is tailored to a specific built-in self-test (BIST) architecture for mixed signal systems. In the BIST architecture under consideration, test pattern waveforms are applied and output metrics are measured [2][13]. Although the current fault simulator is tailored for a specific architecture for BIST, the modular design of the fault simulator permits adaptability to future architectures in future work.

In Chapter 2, we first describe the design of the fault simulator. Then, simulation results for a BiQuad benchmark circuit are given in Chapter 3 and compared with hardware measurements and compared with hand-calculated theoretical results. Finally, Chapter 4 gives suggestions for future directions on the fault simulator.

# **CHAPTER 2: FAULT SIMULATOR DESCRIPTION**

The focus of the fault simulator under consideration is with the analog portion of a mixed signal fault simulator. As discussed in the previous chapter, the more difficult issues are on the analog side, whereas there exist well known methodologies for fault simulation on the digital side. In the following, the analog fault simulator is described. Experimental results using the simulator are presented in the subsequent chapter.

#### 2.1 BIST Framework

The fault simulator takes, as input, a spice net list describing a circuit and simulates randomized versions of the circuit with, and without, faults. The present fault simulator is designed to be used with the built-in self-test (BIST) architecture shown in Fig. 2.1. In the BIST architecture of Fig. 2.1, an input test pattern is generated in digital form in the test pattern generator (TPG), and then converted to an analog waveform in the digital to analog converter (DAC). The circuit under test (CUT) is then excited with this analog waveform. The output of the analog CUT is then converted back to digital format in the analog to digital converter (ADC) and analyzed in the output response analysis (ORA) portion of the system. The ORA then generates the output metrics, or output measures, from the raw data. The ORA data is then used to classify the analog circuit as fault-free or faulty.

Figure 2.1 Built in self test (BIST) framework.

# 2.2 Fault Simulator Functional Flow

The fault simulator was designed to emulate the BIST framework of Fig. 2.1 and simulate the variations in thousands of randomized fault-free and faulty circuits with many different test waveforms (TPG) and different output metrics (ORA). The fault simulator generates the data needed to choose the best possible TPG test vector and best possible output metric, or to choose the best collection of TPG test vectors and output metrics.

In the fault simulator, the input circuit is first parsed into fundamental components, subsequently regenerating randomized versions of the circuit with, and without, faults. The randomizations emulate the normal variations of components in the circuit. The simulator also generates dozens of TPG waveforms to be combined with the randomized circuits, in all possible combinations. Lastly, a separate post processing program is used to convert the output data into histograms of the ORA output metric data to select the best vector and ORA metric and to determine the fault coverage it provides.

The fault simulator is written in the object oriented language of C++ for reusability, platform independence, and low maintenance requirements. The fault simulator is composed of a class library and an executable named faultsim. In addition, SPICE primitives are implemented as class objects in the class library. The C++ compiler and version used is the GNU complier version 3.1, a free ANSI package available to the public, without restrictions. Further details on the class library are found later in section 2.4.

A functional flow diagram of the simulator is given in Fig.2.2. In the first step of Fig. 2.2, the fault simulator takes a SPICE netlist as input. In the second step, the simulator parses the SPICE file into its fundamental components, such as FETS, resistors, capacitors, and inductors. [23].

In the third step of Fig. 2.2, the circuit file components are randomized parametrically and used to create a randomized batch of fault-free circuit files with no catastrophic faults. The randomization in this step is representative of normal variability in component values due to manufacturing processes. Then, faults are inserted by replacing components in the same set of parametrically randomized files with each catastrophic fault possible in the system.

In the "simulation" step of Fig. 2.2, the files are then simulated using the spice engine ELDO, the underlying component in the Accusim package from Mentor Graphics. The fault simulator currently uses Mentor Graphics ELDO, a proprietary product, but can potentially be run on any version of SPICE [24]. Additional inputs to the fault generator step include statistics describing the parametric variation of components and the set of TPG waveforms under consideration.

Figure 2.2 Fault simulator functional flow diagram.

In the next step of Fig. 2.2, Output Response Analysis (ORA), the output response from the simulations are used to compute the output metrics. The fault simulator produces output files including three ORA metrics,  $S_{out}$ ,  $S_{del}$ , and  $S_{mag}$ , found in Table 2.1. In the Table,  $S_{out}$  is the sum of output voltages at each clock cycle for some number, N, of clock cycles. Similarly  $S_{del}$  is the sum of  $V_{out} - V_{in}$  for some number, N, of clock cycles. Similarly,  $S_{mag}$  is the sum  $|V_{out} - V_{in}|$ . The number, N, of clock cycles for the summing of the ORA portion is variable and set at runtime.

Table 2.1

Floating point ORA metrics  $S_{out} = \sum_{r=0}^{N-1} V_{out}[n]$

$$S_{del} = \sum_{n=0}^{N-1} (V_{out}[n] - V_{in}[n])$$

$$S_{mag} = \sum_{n=0}^{N-1} |V_{out}[n] - V_{in}[n]|$$

The summations in the ORA metrics of Table 2.1 are floating point summations that are often useful for the purpose of investigation. However, in actual implementation the output metrics of Fig. 2.1 are necessarily binary, with limited bit resolution. So, in addition to the floating-point values of Table 2.1, the binary equivalents of Table 2.2 are also computed during the fault simulation. These values are then representative of actual ORA data as would be measured in a hardware implementation.

In Table 2.2,  $S_{16out}$ ,  $S_{16del}$ , and  $S_{16mag}$  are binary 16-bit equivalents of the metrics of Table 2.1, where  $((x))_y$  is x modulo y [25]. Hence,  $((x))_{65536}$  is the 16-bit binary representation of x. In Table 2.2,  $S_{16out}$  is the 16-bit binary sum of output voltages and each clock cycle for some number, N, of clock cycles. Similarly  $S_{16del}$  is the 16-bit binary sum of  $V_{out} - V_{in}$  for sum number of clock cycles and  $S_{16mag}$  is the 16-bit binary sum  $|V_{out} - V_{in}|$ . The number of clock cycle durations are variable and set runtime. The analog voltages corresponding to 00 hex and FF hex at the input of the ADC and the output of the DAC in Fig. 2.1 are variables set at runtime.

Table 2.2

Digital ORA metrics

$$S_{16out} = \left( \left( \sum_{n=0}^{N-1} ((V_{out}[n]))_{256} \right) \right)_{65536}$$

$$S_{16del} = \left( \left( \sum_{n=0}^{N-1} \left( \left( \left( \left( V_{out}[n] \right) \right)_{256} - \left( \left( V_{in}[n] \right) \right)_{256} \right) \right)_{65536} \right) \right)_{65536}$$

$$S_{16mag} = \left( \left( \sum_{n=0}^{N-1} \left( \left| \left( (V_{out}[n]) \right)_{256} - \left( (V_{in}[n]) \right)_{256} \right| \right) \right)_{65536} \right) \right)_{65536}$$

For the case of the  $S_{out}$  metric of Table 2.1, the floating point output voltage at each rising edge of the clock is added to the output voltage of each successive clock cycle until the number, N, of user defined TPG clock cycles have elapsed. The  $S_{out}$  ORA metric is then stored. For the case of the  $S_{16out}$  metric of Table 2.2, the 16 bit digital output voltage at each rising edge of the clock is added to the digital output voltage of each successive clock cycle until the number, N, of user defined TPG clock cycles have elapsed. The BIST system has multiple settings for the resolution of the ADC, DAC, and the accumulator. For the purposes of this thesis, the bit resolution of the ADC, DAC, and the final sum are limited to 8, 8, and 16 bits respectively.

The floating point calculation for  $S_{del}$  in Table 2.1 computes floating point  $V_{out}$ - $V_{in}$  at each clock rising edge and sums them for the predetermined number, N, of clock cycles. Similarly, the floating point calculation for  $S_{mag}$  computes floating point  $|V_{out}-V_{in}|$  at each clock cycle and sums them for the predetermined number, N, of clock cycles.

The 16 bit binary calculation for  $S_{16del}$  in Table 2.2 computes 1's compliment  $V_{out}$ - $V_{in}$ . at each clock cycle and sums them for the predetermined number, N, of clock

cycles. The subtraction  $V_{out}$ - $V_{in}$  is implemented using ones compliment subtraction where the two inputs are 8 bit unsigned and the output is 16 bit signed. Similarly, the floating point calculation for  $S_{mag}$  computes floating point |Vout-Vin| at each clock cycle and sums them for the predetermined number, N, of clock cycles.

After the "Output Response Analysis" step of Fig. 2.2, the ORA metrics associated with each circuit file are stored in ORA files that are later post-processed in the histogram generation step. In this final step of Fig. 2.2, histograms are generated showing the distributions of ORA metric values for circuits with, and without, faults. The histogram generation step is a separate software program to post-process the ORA data. From the ORA data, the mean and standard deviation can also be calculated. The end result is the statistical data that can be used to select the most effective TPG test vector and ORA output metric ( $S_{out}$ ,  $S_{del}$ ,  $S_{mag}$ ,  $S_{16out}$ ,  $S_{16del}$ ,  $S_{16mag}$ ), or collection of test vectors and ORA output metrics, for maximum fault coverage.

# 2.3 Fault Simulation Architecture

The overall operation of the fault simulator has been described in the previous section in a functional flow form. This section provides more detail regarding each of the pieces and how they operate together using a more detailed functional flow graph given in Fig. 2.3.

# 2.3.1 SPICE Input

In the first step of Fig. 2.3, the fault simulator reads in the SPICE netlist of the device under test(DUT) of Fig. 2.1. The simulator requires standard SPICE net-list

Figure 2.3 Fault simulator detailed functional flow graph.

format; schematic and VHDL entries cannot be read. SPICE netlist was chosen since it is widely used and standardized interface for describing the DUT of Fig. 2.1.

Spice was developed at the UC Berkley for circuit simulations and is available as open source to the public [23]. SPICE stands for Simulation Program with Integrated Circuit Emphasis. SPICE is a general purpose circuit simulation tool that will run

nonlinear DC, nonlinear transient and linear ac analysis. Circuits written using SPICE can include resistors, capacitors, inductors, mutual inductors, independent and dependent-current and voltage sources, lossy and lossless transmission lines, switches, uniform distributed RC lines, and five most common semiconductor devices; diodes, BJTs, JFETs, MESFETS, and MOSFETS. A SPICE net list file includes but is not limited to information about components, nodal connections, voltage levels, model information, various parameters, and input/output parameters.

#### 2.3.2 Parser

In the second step of Fig. 2.3, the parser takes the circuit and reads each line of the SPICE file. The parser stores all of the information given by the file such as node connections, component values, and other parameters. The parser recognizes components such as R, L, C and converts them into corresponding C++ class library objects, as indicated by the FET, R, L, and C objects below the parser in Fig.2.3 2.3.2.1 Component Statistics

In the upper right of Fig. 2.3, the fault simulator then loads the statistical data required to introduce the parametric variations into the component values. The SPICE file is randomized the number of times specified, with components varied using a uniform or Gaussian distribution according to the specified component statistics. The SPICE netlist file is reconstituted for each catastrophic fault and randomized with the fault by the number of parametric randomizations in the simulation. In this, phase of the simulation, the statistics module of the Faultsim library calculates the appropriate Gaussian distributed values for the components reflecting the tolerances of the corresponding manufacturing processes.

Resistive, inductive, and capacitive components are randomized parametrically according to the default parameters shown in Table 2.3. The components are randomized based on process (i.e., lot-to-lot) statistics and single-chip (i.e., within-a-chip) statistics. A given process will have a Gaussian probability distribution function (pdf) as shown in the top plot of Fig. 2.4. The second plot in Fig. 2.4 shows the pdf of component values on a single chip where the values of the components of a single chip track each other as a result of the processing. This distribution is much tighter, since devices on a single chip will tend to track each other. The bottom plot shows that a distribution for another chip may have a different mean value, but again with the tighter distribution.

Table 2.3 Process statistics

| Component  | Process(chip-to-chip) |   |      | Single-chip(within-a-chip) |   |      |

|------------|-----------------------|---|------|----------------------------|---|------|

|            | statistics            |   | sta  | tistics                    |   |      |

|            | PDF                   | μ | σ    | PDF                        | μ | σ    |

| Resistors  | Gaussian              | 1 | 0.1  | Gaussian                   | 1 | 0.04 |

| Capacitors | Gaussian              | 1 | 0.11 | Gaussian                   | 1 | 0.03 |

| Inductors  | Gauss                 | 1 | 0.12 | Gaussian                   | 1 | 0.02 |

In Table 2.3, the process or, lot-to-lot, variation of resistors are defined with a mean of 1 and a standard deviation of 0.1. This defines a Gaussian distribution of resistor values that vary around their nominal value with a standard deviation of 10 percent. For any given single chip, resistors have a Gaussian distribution center around their nominal value of four percent as indicated by the single-chip statistics column of Table 2.3 with mean 1 and a standard deviation of 0.04 for the resistors. Similarly, capacitor-inductor variation is defined by Table 2.3 for lot-to-lot and single chip.

Figure 2.4 Statistical models showing process pdf (probability density function) in upper trace and two lower traces illustrating single chip pdf's for two different chips. Lower two traces indicate component variations within a single chip or integrated circuit.

In this, it is not likely for the resistors of a chip to be scattered across the full range of lot-to-lot variation. The processing of chips tends to bias component values on a single chip in the same direction giving each chip its own tighter distribution with a standard deviation smaller than lot-to-lot variance. The software implements randomization of chips as illustrated in the two lower plots of Fig. 2.4.

The parser uses as many library modules as needed for reading and faulting the spice net-list files. The library contains classes for implementing resistors, capacitors, inductors, transistors, and different types of sources. When reading a file, if a resistive component is encountered the parser instantiates a Resistor class object from the Faultsim library, which will store the device information for later parsing. Similarly, other SPICE components are implemented as C++ objects in the fault simulation library.

#### 2.3.3 Test Pattern Generation

The upper left of Fig. 2.3 illustrates generating TPG patterns for the fault simulation. The candidate test patterns can be found in Appendix B. These patterns include saw-tooth, frequency sweep, and random waveforms of variable amplitude and frequency. TPG patterns are generated by the TPG class object of the Faultsim library as a piece-wise linear waveform. During simulation, the TPG files are then combined with the aforementioned randomized circuit files generating all possible combinations of parametrically randomized circuits, and TPG waveforms, and faults. The TPG waveforms are stored in files according to waveform, amplitude, and frequency. The clock included in each simulation takes 256 clock cycles(to count through 2<sup>8</sup> bits), to drive the DAC of Fig. 2.1, making the effective waveform frequency equal to the clock frequency divided by 256. This simple relationship between the clock and waveform frequency however is not true for certain waveforms such as frequency sweep. In addition, options in the fault simulator allow for varied number of repetitions for the test pattern waveform, and hold off and time before collecting ORA data.

# 2.3.4 Fault File Generation

In the fault file generation step of Fig. 2.3, hard faults are injected into copies of the original circuit for resistors, capacitors, inductors, and MOSFETS. A resistive catastrophic fault is emulated by placing a  $100 \text{M}\Omega$  in place of the original resistor value for an open, and a  $1\Omega$  resistor for a short. At present, capacitive opens and inductive shorts are simulated as a 2 fF capacitor and 2 fH inductor, respectively. However, capacitive shorts and inductive opens are temporarily implemented as 2 Farad capacitor and 2 Henry inductor, respectively, and remain for future implementations otherwise.

For transistors, the stuck-off transistor level fault emulated by disconnecting the transistor from the circuit with a 100 Meg ohm resistor as shown in Fig. 2.5. The stuck-on transistor level fault is emulated by a 1 ohm resistor between the source and drain of the transistor as shown in Fig. 2.6. [2]

Figure 2.5 Stuck-off fault for transistor illustrating 100 M $\Omega$  series resistor used to implement fault.

Figure 2.6 Stuck-on fault for transistor illustrating 1  $\Omega$  parallel source drain resistor used to implement fault.

# 2.3.5 SPICE Engine

Following the fault file generation step of Fig. 2.3, the SPICE engine used to do the simulation is the Mentor Graphics ELDO tool [24]. The main fault simulator, Faultsim, executable calls ELDO for all simulations using the command "ELDO filename.cir", where filename.cir is the spice file to be simulated. The ELDO simulation

then produces an output file that contains all of the voltage and time data that will be used to calculate the ORA metrics.

#### 2.3.6 ORA

In the next step of Fig. 2.3, once a simulation is complete the six ORA metrics,  $S_{out}$ ,  $S_{del}$ ,  $S_{mag}$ ,  $S_{16out}$ ,  $S_{16del}$ ,  $S_{16mag}$  shown in Table 2.1 and 2.2 respectively, are then computed and stored in an ORA file. The ORA files are organized by TPG waveform for later classification of test vector efficacy and fault coverage. Each ORA file contains all the ORA data for the particular TPG pattern and for all fault conditions. Each line of an ORA file contains eight items; the circuit filename, the test vector name, and the ORA metric values ( $S_{out}$ ,  $S_{del}$ ,  $S_{mag}$ ,  $S_{16out}$ ,  $S_{16del}$ ,  $S_{16mag}$ ) for that combination.

# 2.3.7 Statistical Analysis

In the final step of Fig. 2.3, statistical analysis, the ORA files are post processed using a separate executable program named anarun. The anarun executable is used to produce histograms of the ORA metrics ( $S_{out}$ ,  $S_{del}$ ,  $S_{mag}$ ,  $S_{16out}$ ,  $S_{16del}$ , and  $S_{16mag}$ ) of Table 2.1 and 2.2 which provide a graphical and statistical insight into the efficacy of the test vector. This post-processing tool also computes the mean, standard deviation, and variance of the ORA data, as well as, arrange the data for importation to spreadsheet tools for graphical interpretation as a histogram.

# 2.4 Class Objects

As mentioned beforehand most of the functionality in the fault simulator is implemented as C++ class objects in the Faultsim library. The following sections give brief descriptions of each of the classes and their functions.

#### 2.4.1 Class Resistor

Class Resistor implements the resistor and contains data for the name, resistance value, and nodes of the device. The object also includes statistical parameters, and member functions for reading, writing, and randomizing a resistor.

#### 2.4.2 Class Inductor

Class Inductor works much in the same way that class resistor does. Class inductor contains data for the name, inductance value, and nodes of the devices. The object also includes statistical parameters, and member functions for reading writing, and randomizing a inductor.

# 2.4.3 Class Capacitor

Class Capacitor, much like classes inductor and resistor, contains data for the name, capacitance value, and nodes of the devices. The object also includes statistical parameters, and member functions for reading writing, and randomizing a capacitor.

# 2.4.4 Class Ora

This class object processes the output files from the spice engine, the .chi files, to produce the ORA metrics found in the ORA files. This class contains member functions to search the .chi files for the time and voltage data to compute the output metrics in Table 2.1 and Table 2.2. This class computes the floating point analog ORA metrics as well as the digital metrics. The class object also deletes the rather bulky .chi files after storing the results of the ORA metrics in the ORA files.

#### 2.4.5 Class Gsrc

This class object implements the G-model of spice, or a voltage controlled current source. This class contains member functions to process the nodes of the input and

output along with the transconductance of the model. At present the object does not introduce faults or randomize this component.

#### 2.4.6 Class Vsrc

This class object implements the independent voltage and stimulus source in SPICE. This class contains the data for reading, storing, and writing the nodes and voltage values of independent voltage sources. At present these components do not implement fault or randomization.

#### 2.4.7 Class Circuit

This class handles the circuit level functions of the parser. The class objects loads circuit level objects and segments the tasks of to lower level objects contained therein.

This class contains the data for the complete netlist in the form of a collection of objects appropriate to the corresponding components of the original.

#### 2.4.8 Class DotEnds

This class implements the ".ends" statement that signals the end of a sub-circuit in spice. This object performs the task reading, storing, and writing the ".ends" statements found in SPICE files.

#### 2.4.9 Class Other

This class implements any SPICE token that is not implemented in one of the other class libraries. This class contains the functions and data for reading, storing, and writing all SPICE statements listed in the Other class member functions. These statements include, but are not limited to .ac, .dc, .plot, .print, .probe, .step, .temp etc. There are no functions for faults or randomization in this class.

#### 2.4.10 Class Xsubckt

This class is used for SPICE sub-circuit level statements which typically correspond to one line in a SPICE file. This class contains the member functions for reading, storing, and writing the sub-circuit level statements found in SPICE files.

#### 2.4.11 Class CircuitStats

This class contains the all the functions and data to implement the process (lot-to-lot) and single-chip (within a single Integrated circuit) statistical characteristics of the randomizer as described in section 2.3.2. This class contains a wide array of statistical functions to implement within-chip as well as process (chip-to-chip) pdf's into the randomization of the SPICE file.

#### 2.4.12 Class DotSubckt

Class DotSubckt implements the SPICE statement ".subckt," a definition for a sub-circuit in a SPICE file. This class contains the functions and data for reading, storing, and writing the nodes and names of the sub-circuits of SPICE. This class object has no faults or randomization.

#### 2.4.13 Class Isrc

Class Isrc implements the SPICE independent current source statements found in SPICE files. This class contains the functions and data for reading, storing, and writing the nodes and values of independent current sources. This class has no faults or randomization.

#### 2.4.14 Class Comment

Class Comment implements the comments of SPICE that are denoted by the "\*" character. This class contains the member functions to identify comments, read

comments, and write comments. This class deals only with the contents of comments and therefore has no statistical functions.

#### 2.4.15 Class Esrc

The Esrc implements the SPICE voltage controlled voltage source statements. This class contains the member functions to recognize, read, store, and write E models found in SPICE files. At present, there are no faults or randomization built into this class.

#### 2.4.16 Class Statistics

Class Statistics implements statistical functions that are used in CircuitStats class to generate randomized values from the statistical mean and standard deviation. This class and its member functions do not operate directly on any given component but do serve as support to the process of randomization.

# 2.4.17 Class Component

Class Component identifies each component level object that would be found in a SPICE netlist and acts as a container for particular components. Class component contains the member functions to identify components and execute the proper member classes according to the type of component. This class does not implement statistical randomization or faults.

#### 2.4.18 Class Mos

Class Mos implements the MOSFET component and contains data for the name, channel size, and nodes of the device. The object also includes statistical parameters, and member functions for reading, writing, and randomizing a MOSFET transistor. This class also implements the stuck-on and stuck-off faults illustrated in Figs. 2.5 and 2.6.

#### 2.4.19 Class Faultlist

Class Faultlist implements the generation of fault lists based on the circuit being simulated. This class contains the functions for generating fault lists for shorts and opens of R, L, C, and MOS components.

### 2.4.20 Class Tpg

Class Tpg contains the member functions that create TPG test waveforms based on input parameters of clock frequency, waveform, amplitude, repetitions, and hold off for ORA calculations. The Tpg class generates piecewise linear stimulus in SPICE format and can store the SPICE code in files.

#### 2.4.21 Class Data

Class Data implements the various functions needed for processing generic data arrays used in various places throughout the fault simulator.

# 2.5.1 Computational Complexity

The task of fault simulation presents formidable computational complexity for even modest circuits. To illustrate this complexity, consider the operational amplifier shown in Fig. 4.1, with only 11 components. If each component has two faults, an open and a short, there are 22 potential faults for the circuit. Two hundred randomized netlist files for each fault plus the fault-free file would result in  $(22+1)\times200=4600$  circuit files. If each file is simulated at three frequencies, 10 waveforms, and two amplitudes there are  $(22+1)\times200\times3\times10\times2=276,000$  netlist files to be simulated.

### 2.5.2 Computational Time

The foregoing complexity leads to long computational times. In experiments, the operational amplifier circuit of the previous section has an average simulation time of

eight seconds based on current computing equipment. The computing environment available is a Sun Microsystems SPARC Ultra 80 with four 450 MHz processors and 2 GB of main memory. If the 276,000 circuit files were simulated sequentially this would amount to 25.5 days to simulate the circuits. Also, some waveforms take considerably longer to simulate than others depending on faults and various other conditions such as frequency and amplitude. Therefore, an approximation of the time for simulating the operational amplifier of Fig.4.1 is nearly one month. The linear nature of the problem dictates that doubling the number of components would double the simulation time, meaning a circuit with 22 components would require nearly 2 months to simulate.

### 2.5.3 Parallel Processing

The huge simulation times associated with even small circuits (as outlined in the previous section) provides impetus to use parallel processing in the spice engine portion of Fig. 2.3. This parallelization effort provided for a linear reduction in the amount of time based on the number of parallel threads up to the number of processes on the parallel processing machine. A simulation with two threads ran twice as fast with a simulation with one thread. Experimental results show this to be true when simulating the BiQuad filter shown in Fig. 3.7. The BiQuad filter with 15 components, 160 randomizations, 3 frequencies, and one waveform can be simulated in one day with 4 threads versus 3 days with one thread on a 4-processor machine.

The fault simulator was parallelized by making changes to the main executable faultsim. Parallel threads were implemented with the functions fork() and wait() which spawn parallel processes and close them when they are finished respectively. The program allows a user definable number of parallel processes, threads to be used for a

simulation. The program then creates a process subdirectory for each thread. After the parallel threads finish, the results are then collected and stored in a separate common ORA subdirectory incrementally as the circuit simulations complete for all possible combinations of TPG waveforms, faults, and parametric randomizations.

#### 2.6 Faultsim

Faultsim is the main executable of the fault simulator. Faultsim controls the flow of Fig. 2.2 and Fig. 2.3. The only flow not controlled by faultsim is the post processing executable anarun, the program that generates the histogram for the ORA results as the last steps of Figs. 2.2 and 2.3.

```

%faultsim

faultsim

faultsim usage:

== faultsim čkt.cir numproc numrand inpos inneg outpos outneg vbias

vamp maxcpu

vomin vomax

ckt.cir is the circuit spicefile

numproc is number of processes that are forked()

to run in parallel on a multi-cpu machine

- numrand is number of randomizations per fault

- inpos, inneg are pos and neg differential input nodes

- outpos, outneg are pos and neg differential output nodes

- vbias test pattern dc bias, where

inpos=vbias+(vampl/2),inneg=vbias-(vampl/2)

where inpos=vbias+/-(vampl/2),inneg=vbias

if vbias=0, input is true floating input

- vamp test pattern amplitude in volts

- maxcpu is max number cpu seconds allowed per spice run - vomin to vomax is differential output voltage range

- numrep number or repetitions to execute TPG

Example:

faultsim benchmark.cir 4 4 17 18 16 0 2.5 0.2 120 0 5 1

```

Figure 2.7 Faultsim help screen showing description of command-line parameters and example command-line.

Typing faultsim at the command line, as shown in Fig. 2.7, will display a help screen that lists the command-line parameters and a brief explanation of each. Faultsim is controlled by the following parameters: ckt.cir, numproc, numrand, inpos, inneg, outpost, outneg, vbias, vamp, maxcpu, vomin, vomax, and numrep. The first parameter ckt.cir is the name of the SPICE netlist file that must be in the directory in which faultsim is running. The next parameter, numproc, is the number of processes, or threads that faultsim will spawn in the simulation stage. The parameter numrand is the number of randomizations for each fault and for the good circuit. The parameters inpos and inneg are the node names of the positive and negative input voltages of the SPICE file. These are used to merge the TPG waveforms (as SPICE commands) to the circuit input. The parameters outpos and outneg are the positive and negative output nodes at which the output will be taken and analyzed. The parameter violas is the DC bias level of input TPG waveform. The parameter vamp is the amplitude of the input TPG waveform to be tested. The parameter maxcpu sets the timeout of a single ELDO simulation. This is often necessary as certain faults will cause simulations not to converge or converge slowly. The parameters vomin and vomax set the voltage range of the ADC in the BIST framework. The last parameter, numrep, is the number of repetitions that the simulation will process of each waveform (each repetition being 256 clock cycles).

#### **CHAPTER 3: EXPERIMENTAL RESULTS**

The fault simulator results were compared to theoretical and experimental hardware results for a BiQuad filter. The hardware BiQuad filter was designed and built by Clark Hopper and Steven Tucker working under the direction of Dr. David Binkley.

In this chapter, the fault simulator is validated by comparison to theoretical analysis (hand calculations) and experimental hardware. The focus is on validating the ability of the simulator to predict hardware functionality and therefore a particular TPG waveform is employed which may or may not be the best test vector for this circuit. Nevertheless, the chosen waveform suffices for the purpose of validating the fault simulator.

# 3.1 Biquadratic Filter Circuit

The circuit used for the verification of the fault simulator was a Kerwon-Huelsman-Newcomb biquadratic filter shown in Fig. 3.1[22]. The BiQuad filter has band pass, low pass, and a high pass outputs. The cutoff frequency for all three filter types is set by R and C from the components in feedback of the circuit shown in Fig. 3.1.

$$\omega_o = \frac{1}{RC} = \frac{1}{10k \times .015\mu} = 6.7 \times 10^3$$

(3.1)

Figure 3.1 BiQuad filter circuit used for benchmarking fault simulator against hardware.

Figure 3.2 Frequency response of BiQuad filter shown in Fig. 3.1 with 1 kHz cutoff frequency for high-pass, low-pass, and band-pass.

The cutoff frequency for the experimental hardware is 1 kHz as shown by the frequency response plot of Fig. 3.2. Fig. 3.2 is the frequency response of the circuit of Fig. 3.1, showing the band-pass, low-pass, and high-pass cutoff frequency of 1 kHz. The frequency response plot also shows the circuit has a gain of approximately one half for all the pass band regions. The gain of the BiQuad filter is set by the components R1b and R7 of the circuit shown in Fig. 3.1[22].

$$gain = 2 - \frac{2}{\frac{R_2}{R_3} + 1} = 2 - \frac{2}{\frac{7.5k\Omega}{20k\Omega} + 1} = .55$$

(3.2)

# 3.2 Modeling the BiQuad Efficiently

The BiQuad filter circuit of Fig. 3.1 used to collect hardware experimental results was implemented with AD820A/AD operational amplifier, shown in the operational amplifier circuit of Fig. 3.3.

Figure 3.3 BiQuad hardware implementation using AD820 amplifier.

The AD820A/AD contains 26 transistors each, making the fault simulation of all internal components of the three AD820A/AD amplifiers far too time consuming. Furthermore, the test lab would be unable to test faults at the transistor level for the AD820A/AD package for comparison against fault simulator data. For these reasons, a reduced order model was implemented to emulate the AD820/AD amplifier with a voltage controlled voltage source (VCVS), a current limiting resistor, two diodes and a five volt supply as shown in Fig. 3.4.

Figure 3.4 Emulation of AD820A amplifier used in BiQuad circuit design ideal voltage controlled voltage source, two diodes and output impedance resistor.

In Fig. 3.4, the AD820A/AD is modeled by a (VCVS) along with diodes to cause clipping, and resistive output impedance. In Fig. 3.4, the VCVS emulation of the AD820/AD, the input signals are applied to the positive and negative input nodes of the VCVS. The gain of the VCVS is set to 10<sup>6</sup>. One problem with using the ideal VCVS is the model has no mechanism for clipping, and so the diode network is added to induce clipping. When the output voltage of Fig. 3.4 goes below -.5 volts, which is below the

threshold voltage for the diode, the diode to ground turns on and shorts the output of the circuit to ground. When the output voltage goes above 5.5 volts and breaks the threshold of the diode to the 5-volt supply, the diode limits the output of the E-source to the 5-volt supply. These diodes keep the output of the model of the amplifier, in Fig. 3.4, in the range of 0 to 5 V similar to the AD820A/AD. In future work the 5 V source will be dropped to 4.5 V so the voltage clips at 5 V, similarly the grounded terminal should be set to .5 V so the other rail clips at 0 V.

Another modification to the circuit of Fig. 3.1 included adding an inverting VCVS to the front-end of the BiQuad filter to account for the inverting amplifier used in the experimental hardware, shown following the DAC in the schematic of Fig. 3.18. The VCVS with gain of one, shown in Fig. 3.5, has the input signal connected to the positive input node of the VCVS with the negative input of the VCVS tied to the 5 volt supply.

Figure 3.5 Inverting amplifier for input of BiQuad circuit used to translate 0 to 5 volt input to 5 to 0 volt output. Gain of VCVS is -1.

The circuit of Fig. 3.5, inverts the input signal and adds a 2.5-V DC offset. When the input is 0 volts the output becomes 5 volts, when the input is 5 volts the output will be 0. The negative terminal of the VCVS output is connected to ground and the final output signal of Fig. 3.5 is taken from the positive output. The aforementioned changes to the circuit are to expedite fault simulation by faster circuit simulation times and to provide models representative of the behavior of the original hardware experimental circuit.

Figure 3.18 contains hardware realization used the BIST system of Fig. 2.1. This system was used to obtain the hardware experimental results and was also the model used for the fault simulator. In Fig. 3.18, found at the end of the chapter, the full hardware realization of the fault simulator containing the inverting amp of Fig. 3.5, the DAC and ADC of Fig. 2.1, the BiQuad of Fig. 3.1, and the TPG discussed in section 2.3.3.

# 3.3 Theoretical Results (Hand Calculations)

In this section, theoretical results are presented for several faults, so later these results may be compared with simulation results to validate the fault simulator. In particular, theoretical results are calculated for all six ORA metrics for three faults which produced the same output condition. These three faults were selected because of the simplicity of the hand calculations. The calculations illustrate ORA computation and provide baseline theoretical values for the ORA metrics. For the purposes of discussion and verification, the waveform employed for testing was the count-up waveform (Cup waveform Appendix B) at 19.5kHz effective waveform frequency (5MHz TPG clock frequency), 5 V amplitude, 2.5V DC offset, for one cycle (256 clock cycles) with no hold-off for initialization. Unless otherwise indicated, the remainder of this chapter

discusses results for this TPG waveform with the aforementioned conditions and refer to the high pass output of Fig. 3.1.

# 3.3.1 Calculation for Specific Fault Conditions

For the case of the circuit of Fig. 3.1 without faults, a SPICE simulation showing the input as the lower trace and high pass output as the upper trace is given in Fig. 3.6.

Figure 3.6 SPICE simulation of circuit of BiQuad showing input (lower trace) and output (upper trace). Transient output response due to initial conditions is visible in the output plot.

The saw-tooth waveform in the lower trace in Fig. 3.6 going from 0 to 5 volts at a frequency of 19.5 kHz is the input signal to the BiQuad circuit of Fig. 3.1. The high pass output is the saw-tooth signal in the upper trace of Fig. 3.6, with 2.5 V peak-to-peak centered around 2.5 volts. The 2.5 V peak-to-peak value of the output is consistent with the predicted gain of .5 for the BiQuad circuit. The DC offset of 2.5 in the upper trace of

Fig. 3.6 is also consistent with the expected operation of the BiQuad filter circuit shown in Fig. 3.3, given the 2.5-V virtual ground shown biasing the filter. Although a high-pass circuit should ideally have no DC offset, it can be seen in Fig. 3.6 that the output of the circuit is initially offset above the 2.5 V DC virtual ground, and then levels out centered at 2.5 V around 750μs. This can be attributed to the transients of the circuit, and these effects are later considered in section 3.6 when comparing the ORA metrics with the experimental hardware. Since the simulation was run with no hold off and for only one cycle, these transient effects can be expected to contribute to the measured ORA metrics.

Table 3.1 lists the faults for the BiQuad circuit of Fig. 3.3. From the fault list shown in Table 3.1, three faults were selected that give the output condition of a constant 2.5 volts, as in Fig. 3.7.

Figure 3.7 SPICE plot showing input (lower trace) and output (upper trrace) of faulty BiQuad circuit with 2.5-V DC output condition.

The three faults that produce this 2.5-V constant output condition are R3 short, R2 short, and R1b short shown in Table 3.2 below.

Table 3.1 Fault List for BiQuad filter circuit simulation

| Fault List |       |  |  |  |

|------------|-------|--|--|--|

| Component  | Fault |  |  |  |

| R3         | Open  |  |  |  |

| R3         | Short |  |  |  |

| R4         | Open  |  |  |  |

| R4         | Short |  |  |  |

| R5         | Open  |  |  |  |

| R5         | Short |  |  |  |

| R6         | Open  |  |  |  |

| R6         | Short |  |  |  |

| R2         | Short |  |  |  |

| R7         | Open  |  |  |  |

| R7         | Short |  |  |  |

| C1         | Open  |  |  |  |

| C2         | Open  |  |  |  |

$\label{eq:table 3.2} \text{List of Specific Components and Faults for ORA Confirmation were $V_{out}$ is a constant 2.5 $VDC$}$

| Component | Fault | Output Condition |

|-----------|-------|------------------|

| R2        | Short | 2.5 volts        |

| R3        | Short | 2.5 volts        |

| R1b       | Short | 2.5 volts        |

The SPICE simulation of the three fault conditions shown in Table 3.2 produced the output (2.5-VDC) shown in the upper trace of Fig. 3.7, with a saw-tooth input shown in the lower trace. These faults were chosen because they offer easily calculated ORA metrics.

# 3.3.1.1 S<sub>out</sub> Floating Point Calculation

The cases of Table 3.2 with an output voltage stuck at 2.5 V and with the input going from 0 to 5 volts over 256 clock cycles is a useful condition for validation since it provides simple hand calculations. In this case,  $S_{out}$  becomes:

$$S_{out} = \sum_{n=0}^{N-1} V_{out}[n] = \sum_{n=0}^{255} 2.5 = 256 \times 2.5 = 640$$

.

For more complex signals, the summation can be viewed as an integral or area under the  $V_{out}$  curve. For the present example, the  $S_{out}$  metric is analogous to the area of the rectangle (i.e. the integral of the rectangle) shown in Fig. 3.8. Given that the result is

Figure 3.8 Illustration showing area corresponding to the fault for 2.5-V output condition of Fig. 3.7 over 256 clock cycles for computing  $S_{out}$  metric. The area is  $2.5 \times 256 = 640$ .

for one TPG waveform cycle only (256 clock cycles), Sout would equal the area of a

rectangle with base=256 clock cycles and height=2.5 V with area 256x2.5=640. This is the area of the rectangle in Fig. 3.8.

### 3.3.1.2 S<sub>del</sub> Floating Point

The cases of Table 3.2 with an output voltage stuck at 2.5 V are used for  $S_{del}$  since it provides simple hand calculations. The  $S_{del}$  metric subtracts the voltage of the input from the output voltage at each clock cycle and sums the result over the number of specified clock cycles. Only one cycle of the TPG waveform (256 clock cycles) is used for the simulation under consideration. In the upper left of Fig. 3.9,  $V_{out}$  is represented as a 2.5-VDC constant for 256 clock cycles. In the upper right,  $V_{in}$  is represented as a ramp from 0 to 5 volts for those same 256 clock cycles. At the bottom is the difference of the upper two figures representing  $V_{out}$  – $V_{in}$  for same 256 clock cycles. In this case,  $S_{del}$  becomes:

$$S_{del} = \sum_{n=0}^{N-1} (V_{out}[n] - V_{in}[n]) = \sum_{n=0}^{255} \left( 2.5 - \frac{5n}{255} \right) = 256 \times 2.5 - \sum_{n=0}^{255} \frac{5n}{255} = 0.$$

For more complex signals, the summation can be viewed as an integral or area under the  $V_{out}$  -  $V_{in}$ . For the present example, the  $S_{del}$  metric is analogous to the area under the curve at the bottom of Fig. 3.9. Given that there is equal positive and negative area under the curve of Fig. 3.9, the net result should be at or near 0.

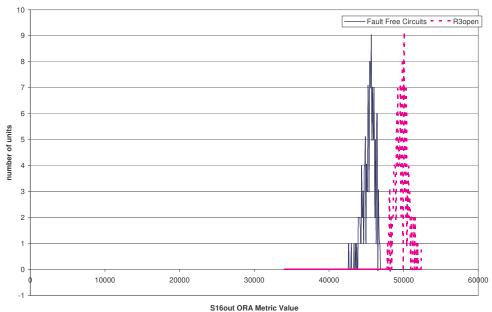

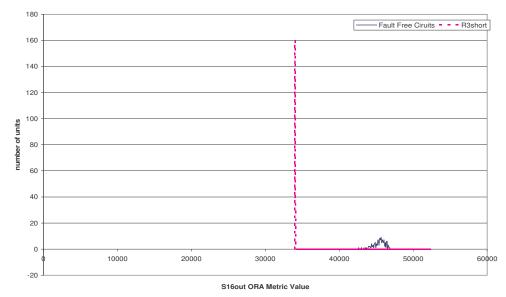

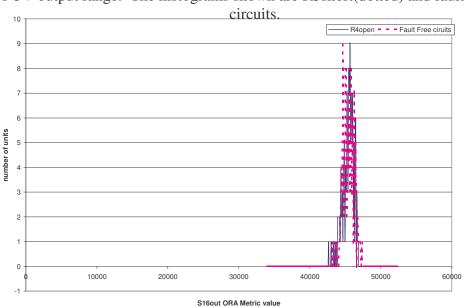

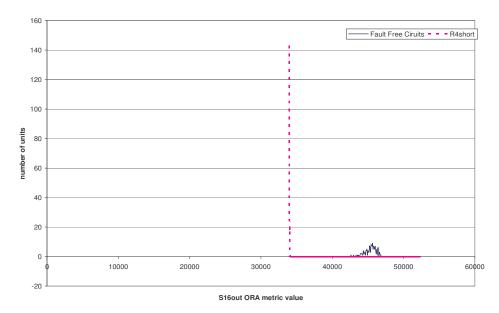

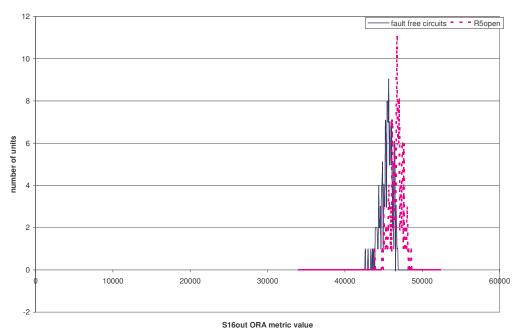

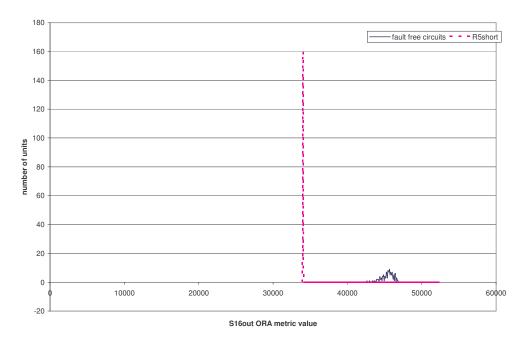

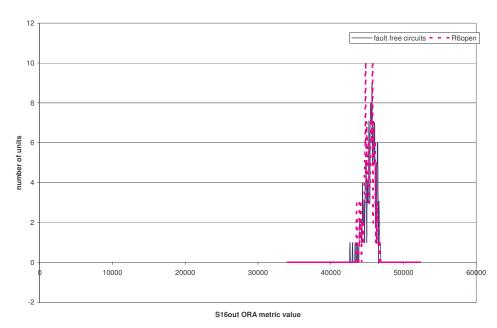

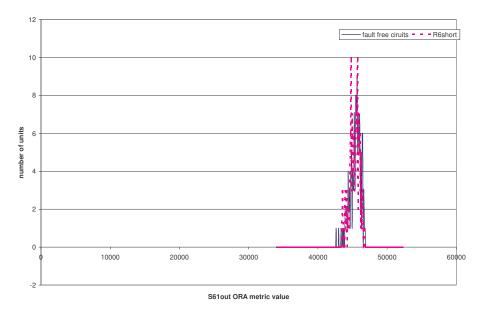

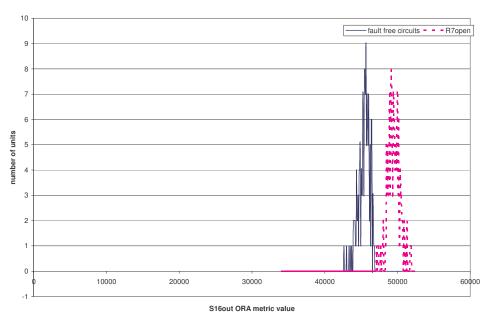

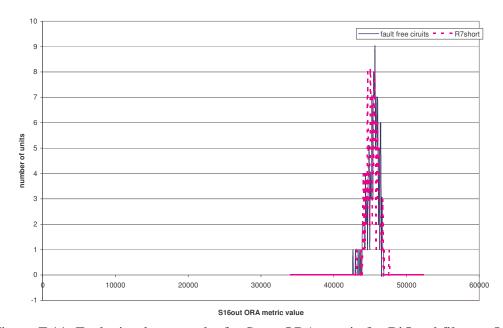

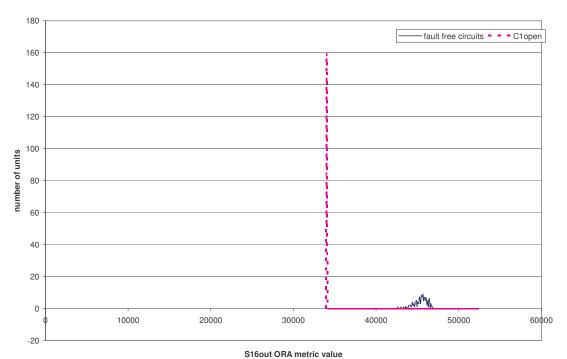

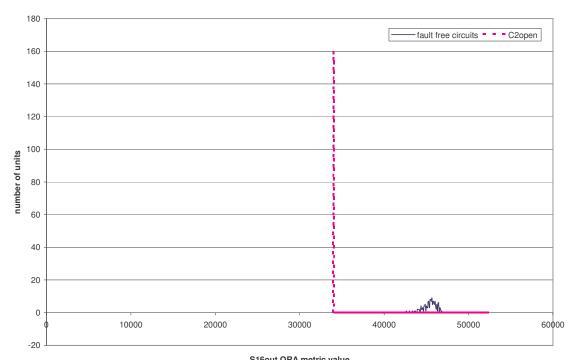

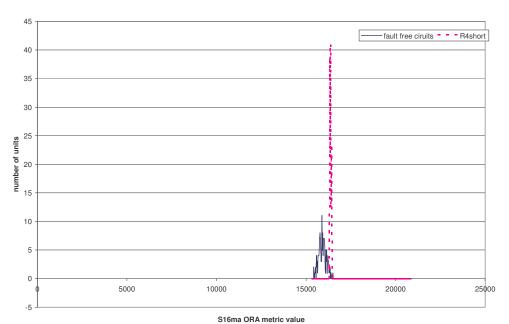

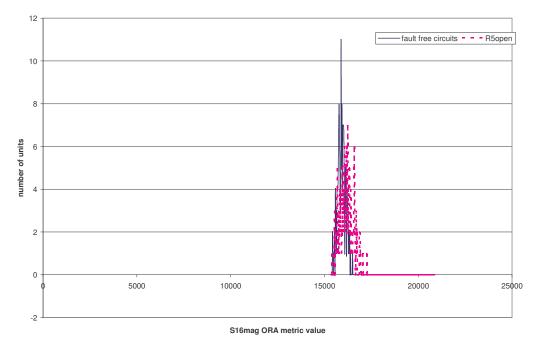

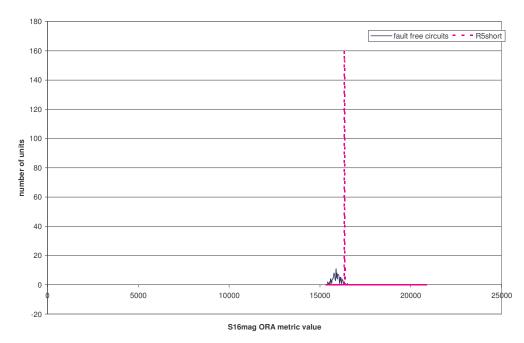

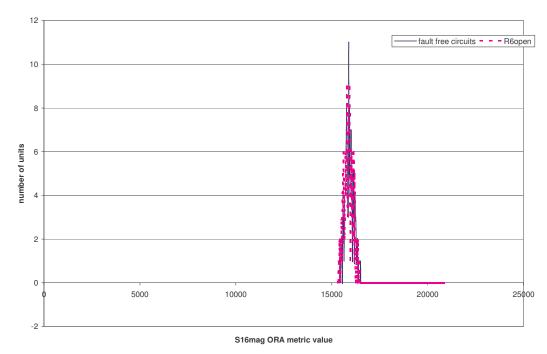

### 3.3.1.3 S<sub>mag</sub> Floating Point