Microwave Circuits and

Metamaterials

Project 14

Overview

Remain in same project groups for the

semester.

The objective of this project is to investigate CMOS non-Foster

circuits using current conveyors and the ADS simulator.

NOTE: Use the Project Report Template and keep answers to questions on consecutive sheets

of paper with all plots at the end.

IN NO CASE may code or files be exchanged between students, and

each student must answer the questions themselves and do their own

plots, NO COPYING of any sort! Nevertheless, students are

encouraged to collaborate in the lab session.

Only turn in requested plots ( Pxx )

and requested answers to questions ( Qxx ).

Part 1

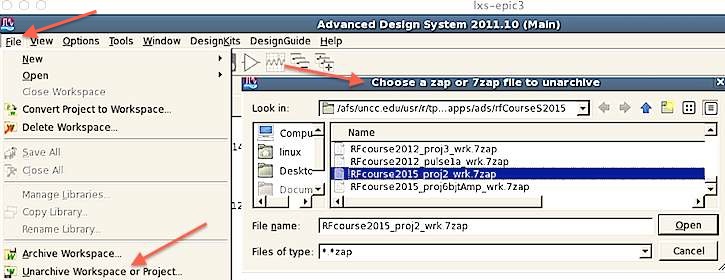

- Load and run the CMOS Current conveyor example as follows:

- This project does not seem to function

properly when downloaded as a zip-file, so it must be

downloaded as a 7zap archive as follows:

- You should find a new RFcourse2015_proj14nonFosCurConv_wrk

directory created in apps/ads

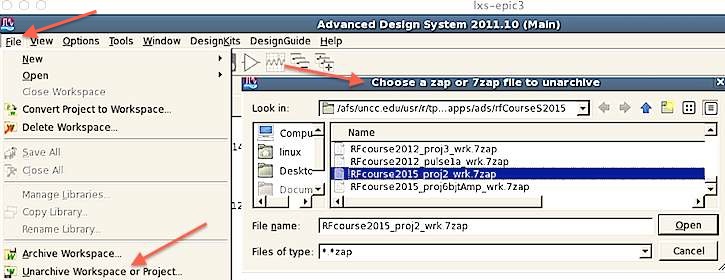

- Go down through the directory tree to cmosCurConv_a

and double click that design file, and the following

schematic should appear.

- Run the simulation, and annotate the

dc voltages on the schematic, using

MenuBar::Simulate::AnnotateDc. Save a snapshot of

the schematic and paste it into your report.

( P1 )

- Make sure that your

plots, component

values,

legends, axes, and fonts are legible in your report!

- For snapshots use the

Linux menu Graphics::Ksnapshot and select the option

to take a legible snapshot of a window rather than full screen

- What size (length and width) are the wn50 NMOS

transistors? Hint: select the transistors and

push-into-hierarchy (red circle above)(

Q1 )

- What size (length and width) are the wp100 PMOS transistors?

Hint: select the transistors and push-into-hierarchy (red

circle above)( Q2 )

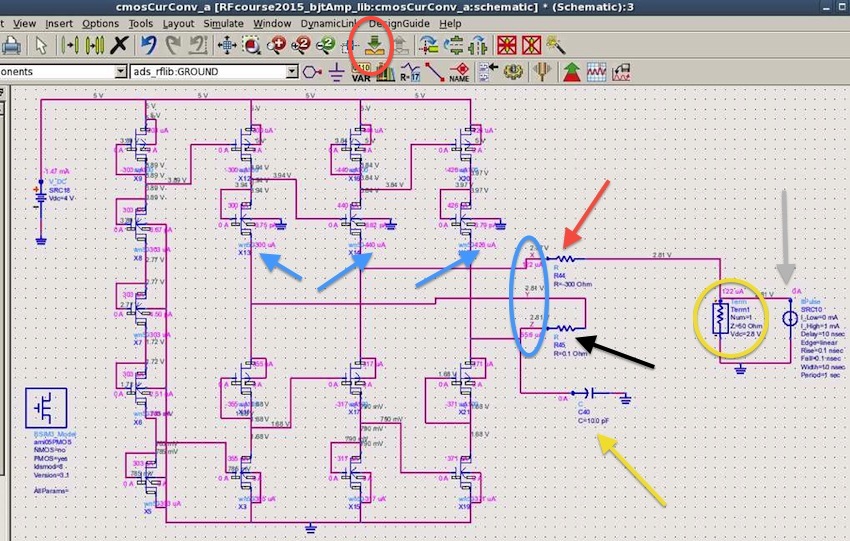

- Run the simulation

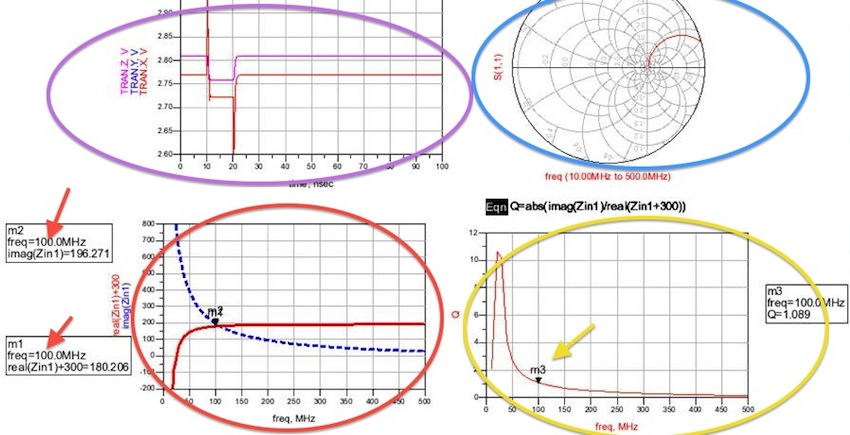

- You should see a number of plots as follows:

- Save a snapshot of the real and imaginary parts of Zin (red

circle above), also with 2 markers (red

arrows) at 100 MHz as illustrated

above. ( P2 )

- Does the imaginary part of input impedance Zin1 in the red

circle above follow the proper shape for a negative

capacitor? yes/no ( Q3 )

- What is the real part of input impedance Zin1 at 100 MHz

(red arrows above)? ( Q4 )

- What is the imaginary part of input impedance Zin1 at 100

MHz (red arrows above)? ( Q5 )

- What is the quality factor of the input impedance Zin1 at

100 MHz (red arrows above)? Hint: quality factor Q =|

imag(Zin1)/real(Zin1) | . ( Q6 )

- Save a snapshot of the Q plot (yellow circle above), also with 1 marker at the

frequency where Q=1 as

illustrated above. ( P3 )

- What is the effective negative capacitance corresponding to

the imaginary part of input impedance Zin1 at 100 MHz (red

arrows above)? ( Q7 )

- Compare this capacitance to C40 and in light of eqution (9)

in Comparison

of CMOS Current Conveyor Circuits for Non-Foster

Applications. ( Q8 )

- Note that R44 is set to -300 so that

the negative capacitance will be stable under measurement,

therefore 300 ohms are added to the plot of the real(Zin) to

compute Zin.

- Why is R44 set

to 300 ohms? ( Q9 )

- Why is 300 ohms

added to the plot of real(Zin)? (

Q10 )

- Save a snapshot of the Smith chart (blue circle above), also with 2 markers at 50 and

250 MHz . ( P4 )

- Note that this plot is outside the normal Smith chart,

because the real(Zin) is negative, a negative

resistance. The outer boundary of the "normal" Smith

chart is impedances of the form "Z=0 + j x,'" where the

resistive part equals zero. This

is because of the -300 ohms added in series with the

input. Hence, the smith chard does not reflect the

input impedance of the circuit for this project.

- Finally plot the time-domain signal (purple circle

above). ( P5 )

The current source in the schenatic injects a small pulse to

check if the circuit is stable.

- R44

stabilizes the circuit. Set R44 to 1 ohm, and...

- rerun the simulation

- Re-plot the time-domain signal (purple circle above).:

- Save a snapshot of the unstable time-domain

(purple circle above), and paste it into your report. ( P6 )

- Save a snapshot of the unstable

real/imag of Zin (red circle above), and paste it into your

report. ( P7 )

- Did the circuit

instabiltiy manifest itself as oscillation or

"latch-up?" (

Q11 )

- Because of the potential for oscillation in non-Foster

circuits, one should always run a time-domain simulation to

check stability.

- Return the resistor R44 to -300 ohms

- Set C40 to 5 pF to observe the change

in the input impedance

- Rerun the simulation

- Save a snapshot of the real and imaginary parts of Zin (red

circle above), also with 2 markers (red

arrows) at 100 MHz as illustrated

above. ( P8 )

- What is the imaginary part of input impedance Zin1 at 100

MHz (red arrows above)? ( Q12 )

- Compare this capacitance to C40 and in light of eqution (9)

in Comparison

of CMOS Current Conveyor Circuits for Non-Foster

Applications. ( Q13 )

- Based on the paper Parasitic

Resistance in Non-Foster Circuits Caused by Current Conveyor

Frequency Response, frequency response of the

transistors causes the parasitic resistance in the current

conveyor. In equation (10) of this paper, which term in

the equarion corresponds to the parasitic resistance, and what

do the variables "omega-sub-zero" and C represent?( Q14 )

NOTE ReportTemplate: Use the Project Report Template

and keep answers to questions on

consecutive sheets of paper with all plots at the end.

Do not add extraneous pages or put explanations on separate

pages unless specifically directed to do so. The instructor will

not read extraneous pages!

Only turn in requested plots (Pxx )

and requested answers to questions (Qxx ).

All plots must be labeled P1, P2, etc. and all questions must be

numbered Q1, Q2, etc. YOU MUST ADD CAPTIONS AND FIGURE

NUMBERS TO ALL FIGURES!!

Copyright 2010-2015 T. Weldon

Cadence, Spectre and Virtuoso are registered trademarks of

Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA

95134. Agilent and ADS are registered trademarks of Agilent

Technologies, Inc.