Part 2

What is the transconductance of the MOSFETS in the differential pair? ( Q9)

Part 3

Layout the whole amplifier, without a padframe. This layout will be a "rough layout," so you do not need to eliminate all DRC errors or all overflows.

Fold the two fets by first carefully selecting the two poly gate pins and then Palette-->DLADevice-->Edit-->Fold and enter 8.

On the folded FETS, make one source and drain and gate contact (for this rough layout do not bother to connect all the drains together, sources together, and gates together).

Autoroute your layout, leaving a few overflows in the FETs. (You would need to complete all of the routing if this was a design going to fabrication).

Use compaction to shrink the layout, and check it with DRC (design rule

check). To get the compactiobn menu, leave the ADK Palette by

clicking "Top" and then select the "Place and Route" Palette.

Click "Compact" and use the "Box" tool to restrict

compaction to the desired area of your circuit. Compact

in the UP/Down/Right/Left as needed. Make sure to run DRC to

see any errors induced by compaction. (Run DRC outsidce the region

where BJTs are to avoid the BJT errors.)

Print the layout.

Note: AMI 1.2 micron process DRC may not be completely functional, since it may not recognize BJT's properly. ( P14 )

run IcTrace(M) to do LVS and see the report. Anything other than a smiley face is no good. Use a schematic with all the grounds connected together for the schematic (and use the lvs viewpoint as the source file for comparison!)

Note: AMI 1.2 micron process LVS is not completely functional, since it does not recognize resistors properly.

Only AFTER you finish ALL connections in the circuit: Use "Object->Add Overflow" to add overflows to connect the amplifier input and output to analog pins on the padframe. You must be very careful to "hit the right spot" on the analog pin.

To add overflows you must enter connectivity edit mode (CE) by the command Context:SetCellConfig:ConnectEdit, then add overflows as Object:Add:Overflow.

Also add overflows connecting the amplifier ground pin to the padframe ground pin. Connect the amplifier power using a overflow to another analog ground pin. The padframe power supply may be too noisy for an anolog circuit, if there are digital circuits on-chip. Use the autorouter to route the 4 overflows created above.

Finally, add a metal-1 strap to short out one of the resistors built into the analog pad connected to the amplifier power supply. Print the layout. ( P15 )

Reset IC station to Correct by Construction editing mode by using: Context:SetCellConfig:CorrectbyConstruction

Note: do not "connect by hand," always route using overflows and the autorouter. 90% of bad chips are do to errors when routing/connecting "by hand."

To check that your GDSII was written properly, close all Mentor tools. Then open a new ICstation and run MenuBar-->Translate-->ReadGDSII to check the file. Show your GDS-II layout to the instructor and have him sign the layout that was printed out, verifying that a GDS-II tapeout was completed. ( Q13 )

Part 4

The decoder follows the general design in Figs. 17.12 and 17.13. The SRAM cell follows Fig. 17.2. What happens to the decoder outputs (D0-D7) when the enable line is low? ( Q14 )

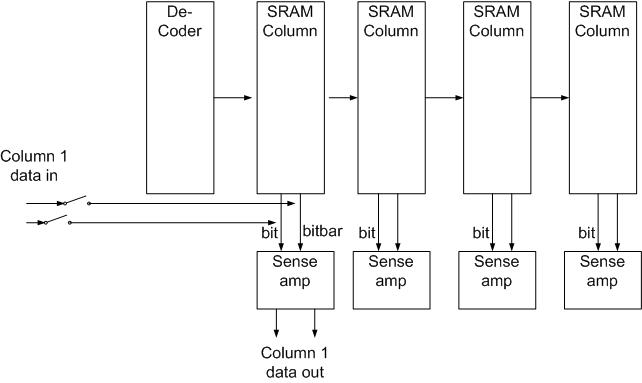

A rough block diagram would be:

where two switches (see later) are used to disengage the data in lines during read operations. Output data during read is taken directly from the sense amps.

For sense amplifiers, the timing of a read cycle is:

_____ Data is ready here

|

v

______

clock |______| |

______

prechargebar |______| |

______

sense | |______|

______

decoder enable |______| |

In the first half cycle:When prechargebar is low, bit and bitbar are pulled high, precharging both bit and bitbar to a high voltage while the sram cells are disabled because the decoder enable is held low. At the same time, the sense line is high, turning off any connection between the senseamp and bit or bitbar. Also, the bottom transistor in the senseamp is on, so the senseamp is on, and the data out (dat) is from the prior cycle.

in the second half cycle:

The prechargebar goes low, disconnecting the precharge of bit/bitbar,

and the decoder is enabled to dump the ram contents onto the bit/bitbar lines.

At the same time the sense line causes thesense amp bottom transistor to turn off,

and the series fets on bit and bitbar to be turned on. During this time

the sram cell contents tend to charge/discharge bit/bitbar cusing a stored

voltage difference inside the senseamp (which is turned off because

of the bottom transistor).

at the very end, when the senseamp goes high again, the stored charge internal to the senseamp from bit/bitbar determines the state of the data output (dat) for the following half-cycle.

Note: do not use decoders at the sense amplifier outputs at the bottom of Figure 17.11 on page 341, in the Data selector/decoder. Assume that the system uses 4-bit-wide words, so you want all 4 bits as output (rather than demultiplexing with the Data selector/decoder at the bottom of Fig. 17.11).

Do NOT use the amplifier in Fig. 17.10 of page 340 with minimum size easyfets (except the two precharge precharge devices should be 2x as wide).

For precharge, use the methods of Figs 17.9 and 17.10.

Include switches on the 4 data input pins, using the transmission gates of Fig. 13.1 on page 255, with devices 2x as wide as the smallest easy-fet. The use of these will allow you to more easily test your SRAM in Accusim. The switches isolate the the data inpput sources from the bit/bitbar lines during a read operation.

For the write operations, the switch should be on and you drive the data ports with external voltage sources. For the read operation you can turn the switches off, effectively decoupling the voltage sources so you can monitor the internal workings of the chip to see if the data was indeed stored. For convenience, you MUST add input/output ports on both sides of the switches to your schematic, so it is easier to see these signals in accusim. Also, for convenience it is easiest to use separate input and output pins for the data (rather than a single bidirectional pin for input output).

When you finish the design, print out a copy of your schematic, clearly labeling the required pins defined above. ( P19 )

Show a simulation in accusim of successively writing and reading data "1111" and "0000" to memory addresses 000, and 001 ( P20 )

Part 5

But first: are your outputs suized properly to drive the pads?? See section 11.4 and assume your output pad is 5 pF. (Also see Weste and Eshraghian p. 219). What is the optimum sizing ratio in successive stages of a chain of buffers (what is A in Eq. 11.22) ? ( Q15 )

Note: in general, do not "connect by hand," always route using overflows and the autorouter. 90% of bad chips are do to errors when routing/connecting "by hand."

Use compaction to reduce size. Makes sure it passes DRC. (Compaction tends to crash, so save your work often!)

Report

Write any comments or observations you may have directly on the printouts. Type or clearly handwrite. Do not add extraneous pages or put explanations on separate pages unless specifically directed to do so. The instructor will not read extraneous pages!

Only turn in requested plots ( Pxx ) and requestes answers to questions ( Qxx ). All plots must be labeled P1, P2, etc. and all questions must be numbered Q1, Q2, etc.

Turn in a separate sheet with answers to all of the specific questions above.

Turn in all requested plots ( Px ). Place answers to all questions ( Qx ) on a separate sheet of paper, with questions consequitively numbered. Keep answers to questions only 2 or 3 sentences long, or 2 or 3 lines of computation, in most cases. 2 or 3 sentences should suffice for most explanations. All plots must be labeled P1, P2, etc. and all questions must be numbered Q1, Q2, etc.

Only turn in requested plots ( Pxx ) and requested answers to questions ( Qxx ).